-

【软件架构文档之SOC篇】

软件系统设计SOC介绍

ZYNQ 5EV 包含APU4(arm cortex A53),RPU2(arm cortex R5),OCM(内部存储器),PMU, Perepherals,GPU,CSU.

其中PS系统部分的主要参数如下:

① ARM四核Cortex-A53处理器,速度高达1.2GHz,每个CPU32KB 1级指令和数据缓存,1MB 2级缓存CPU共享。

② ARM 双核Cortex-R5处理器,速度高达600MHz,每个CPU 32Kb 1级指令和数据缓存,及128K紧耦合内存。

③ 图像视频处理器Mail-400 MP2,速度高达600MHz,64KB 2级缓存。

④ 外部存储接口,支持32/64bit DDR4/3/3L、LPDDR4/3接口。

⑤ 静态存储器接口,支持NAND,2xQuad-SPI FLASH。

⑥ 高速连接接口,支持PCIe Gen ,USB3.0,Sata 3.1,DisplayPort,Ethernet.

⑦ 普通连接接口,USB2.0,SDIO,UART,CAN,I2C,SPI,GPIO.

⑧ 电源管理:支持 Full/Low/PL/Battery四部分电源的划分。

⑨ 加密算法:支持RSA,AES和SHA。

⑩ 系统监控:10位1Mbps 的AD采样,用于温度和电压的监测。

其中PL逻辑部分的主要参数如下:

① 逻辑单元

② 触发器

③ 查找表

④ Block Ram

⑤ 时钟管理单元

⑥ DSP Silces

⑦ 图像编解码单元

⑧ PCIE3.0

⑨ GTH总线连接图

SOC内部总线具有监控与隔离功能.

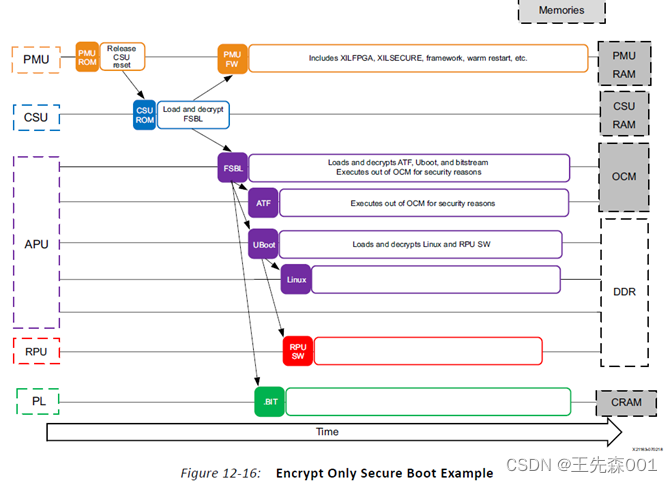

SOC启动图

上电先完成PMU与CSU硬件启动,然后完成FSBL的软件启动,FSBL可运行在A0核或者R0核。

PS和PL的互联技术

ZYNQ作为高性能ARM Cortex-A53 系列处理器与高性能FPGA在单芯片内紧密结合的产品,为了实现ARM处理器和FPGA之间的高速性能处理器与FPGA之间的互联通路。因此,如何设计高效的PL与PS数据交互通路是ZYNQ芯片设计的重中之重,也是产品设计的成败关键之一。

AXI全称Advanced eXtensible Interface,是Xilinx从6系列的FPGA开始引入的一个接口协议,主要描述了主设备和从设备之间的数据传输方式。AMBA(Advanced Microcontroller Bus Architecture)的一个部分,是一种高性能、高带宽、低延迟的片内总线,也用来替代以前的AHB和APB总线。

AXI协议主要描述了主设备和从设备之间的数据传输方式,主设备和从设备之间通过握手信号建立连接。当从设备准备好接收数据时,会发出READY信号。当主设备的数据准备好时,会发出和维持VALID信号,表示数据有效。数据只有在VALID和READY信号都有效的时候才开始传输。当这两个信号持续保持有效,主设备会继续传输下一个数据。主设备可以撤销VALID信号,或者从设备撤销READY信号终止传输。

ZYNQ中,支持AXI-Lite,AXI4 和AXI-stream三种总线。

AXI4-Lite:

具有轻量级,结构简单的特点,适合小批量数据、简单控制场合。不支持批量传输,读写时一次只能读写一个字(32bit)。主要用于访问一些低速外设和外设的控制。

AXI4:

接口和AXI-Lite差不多,只是增加了一项功能就是批量传输,可以连续对一片地址进行一次性读写。也就是说具有数据读写的burst功能。

AXI4-Stream:

这是一种连续流接口,不需要地址线(很像FIFO,一直读或一直写就行)。对于这类IP,ARM不能通过上面的内存映射方式控制(FIFO根本没有地址的概念),必须有一个转换装置,例如AXI-DMA模块来实现内存映射到流式接口的转换。S_AXI_HP{0:3}_FPD接口,是高性能/带宽的AXI4标准的接口,总共有四个,PL模块作为主设备连接。主要用于PL访问PS上的存储器(DDR和FPDMain Switch)。

S_AXI_LPD接口,高性能端口,连接PL到LPD。低延迟访问OCM和TCM,访问PS端DDR。

S_AXI_HPC{0,1}_FPD接口,连接PL到FPD,可连接到CCI,访问L1和L2Cache,由于通过CCI,访问DDR控制器会有较大延迟。

M_AXI_HPM{0,1}_FPD接口,高性能总线,PS为master,连接FPD到PL,可用于CPU, DMA, PCIe等从PS推送大量数据到PL。

M_AXI_HPM0_LPD接口,低延迟接口总线,PS为master,连接LPD到PL,可直接访问PL端的BRAM,DDR等,也经常用于配置PL端的寄存器。

只有M_AXI_HPM{0,1}_FPD和M_AXI_HPM0_LPD是Master Port,即主机接口,其余都是Slave Port(从机接口)。主机接口具有发起读写的权限,ARM可以利用两个主机接口主动访问PL逻辑,其实就是把PL映射到某个地址,读写PL寄存器如同在读写自己的存储器。其余从机接口就属于被动接口,接受来自PL的读写,逆来顺受。在PS与PL互联应用,用的最多的接口为S_AXI_HP{0:3}_FPD、M_AXI_HPM{0,1}_FPD和M_AXI_HPM0_LPD。

AXI协议严格的讲是一个点对点的主从接口协议,当多个外设需要互相交互数据时,我们需求加入一个AXI interconnect IP模块,也就是AXI互联矩阵,作用是提供一个或多个AXI主设备连接到一个或多个AXI从设备的一种交换机制。

AXI Interconnect基本连接模式有以下几种:

1.多对一的情况

2.一对多的情况

3.多对多读写地址通道

4.多对多读写数据通道ZYNQ的内部AXI接口设备就是通过互联矩阵的方式互联起来的,既保证了传输数据的高效性,又保证了连接的灵活性。

ZYNQ芯片开发流程

由于ZYNQ将CPU与FPGA集成在了一起,开发人员既需要设计ARM的操作系统应用程序和设备的驱动程序,又需要设计FPGA部分的硬件逻辑设计。开发中既要了解Linux操作系统,系统的构架,也需要搭建一个FPGA和ARM系统之间的硬件设计平台。所以ZYNQ的开发是需要软件人员和硬件硬件人员协同设计并开发的。这既是ZYNQ开发中所谓的"软硬件协同设计”。

Vivado设计套件实现FPGA部分的设计和开发,管脚和时序的约束,编译和仿真,实现RTL到比特流的设计流程。

Xilinx SDK(Software Development Kit),SDK是Xilinx软件开发套件(SDK),在Vivado硬件系统的基础上,系统会自动配置一些重要参数,其中包括工具和库路径、编译器选项、JTAG和闪存设置,调试器连接已经裸机板支持包(BSP)。SDK也为所有支持的Xilinx IP硬核提供了驱动程序。SDK支持IP硬核(FPGA上)和处理器软件协同调试,我们可以使用高级C或C++语言来开发和调试ARM和FPGA系统,测试硬件系统是否工作正常。

ZYNQ的开发也是先硬件后软件的方法。具体流程如下:- 在Vivado 上新建工程 ,增加一个嵌入式的源文件;

-

在Vivado 里添加和配置PS和PL部分基本的外设,或需要添加自定义的外设;- 1

- 在Vivado里生成顶层HDL文件,并添加约束文件。再编译生成比特流文件(*.bit);

- 导出硬件信息到SDK软件开发环境,在SDK环境里可以编写一些调试软件验证硬件和软件,结合比特流文件单独调试ZYNQ系统;

- 在SDK里生成FSBL文件;

- 在sdk里通过FSBL文件,比特流文件system.bit和u-boot.elf文件生成一个BOOT.bin文件;

ZYNQ固化程序流程

普通的FPGA一般是从flash启动,或者被动加载,ZYNQ的启动是由ARM主导的,包括FPGA程序的加载,ZYNQ MPSoc启动一般为三个步骤:

Pre-configuration stage:预加载阶段由PMU控制,执行PMU ROM中的代码设置系统。PMU处理所有的复位和唤醒过程。

Configuration stage :接下来最重要的一步,当BootRom(CSU ROM代码的一部分)搬运FSBL到OCM后,处理器开始执行FSBL代码,FSBL主要有以下几个作用:- 初始化PS端配置,MIO,PLL,DDR,QSPI,SD等

- 如果有PL端程序,加载PL端bitstream

- 搬运用户程序到ddr,并执行跳转执行

Post-configuration stage:FSBL开始执行后,CSU ROM代码进入Post-configuration阶段,负责起系统干预响应,CSU为验证文件正确性、通过PCAP加载PL、存储管理安全密钥、解密等提供持续的硬件支持。

第一个文件一定是BootLoader,就是fsbl.elf;第二个文件就是FPGA的配置文件,bitstream;第三个程序就是应用程序。

-

相关阅读:

[管理与领导-83]:IT基层管理者 - 核心技能 - 高效执行力 - 8- 提升执行力的三大方法:目标复述、任务分解、寻求帮助

个税计算、税基的处理

DeepStream--测试resnet50分类模型

【Shell编程】字符截取命令awk、sed命令

使用UiPath和AA构建的解决方案 1. 机器人过程自动化入门

postman 之接口关联

flex的用法 代码6

Unity之UI、模型跟随鼠标移动(自适应屏幕分辨率、锚点、pivot中心点)

LeetCode 两数之和 & 三数之和& 四数之和

30天Python入门(第十九天:深入了解Python中的文件处理)

- 原文地址:https://blog.csdn.net/qq_35968965/article/details/125405825