-

VCS编译bug汇总

‘typedef’ is not expected to be used in this contex

注册前少了分号。

Scope resolution error

resolution : 声明指针时 不能与类名同名,即 不能声明为adapter.

cannot find member "type_id"

忘记注册了

拼接运算符使用

关键要加上1'b,不然拼出来只有1bit

Error casting p_sequencer, please verify that this sequence/sequence item is intended to execute

在搭建UVM环境的时候出现这个错误,发现seq0里面 调用了`uvm_declare_p_sequencer(my_vsqr) 和seq0.start(p_sequencer.p_sqr0);不一致导致的

将seq0.start(p_sequencer.p_sqr0)改成seq0.start(p_sequencer)

SystemVerilog中forever begin end導致的Hang死

- forever begin

- if(expre == 1) begin

- run();

- end

- end

1、如果run()這個task值耗時的,當if條件成立時,不會hang死。

2、如果if條件不成立,肯定會hang死。

3、防守的辦法是給if條件後面加上else分支,在else中做一個延時:@axi_if_cb;如果if條件不成立,走一T再進行下一次判斷:

- forever begin

- if(expre == 1) begin

- run();

- end

- else begin

- @axi_if_cb;

- end

- end

寄存器模型同时访问

图中两个寄存器值都是32'h1d,注释中的方式访问得到的1d而非正确值0000001d0000001d。因为同时访问丢失了一个,得到的值是0.

找不到顶层tb

特别离谱,filelist,模块名和makefile都没问题。

- $COMMON_ROOT/vip/tue-master/src/*

- $COMMON_ROOT/vip/tue-master/src/tue_pkg.sv

- $COMMON_ROOT/vip/tvip-axi-master/scr/tvip_axi_pkg.sv

- $COMMON_ROOT/vip/yuu_pkg/yuu_common/include/yuu_common_pkg.sv

- $COMMON_ROOT/vip/yuu_pkg/yuu_amba_bak/include/yuu_amba_pkg.sv

- $COMMON_ROOT/vip/ahb_vip/ahb_include/yuu_ahb_pkg.sv

- $COMMON_ROOT/vip/apb_vip/apb_include/yuu_apb_pkg.sv

- $K1_SOC_ROOT/verf/bt/bt_k1/env/k1_env_pkg.sv

- $K1_SOC_ROOT/verf/bt/bt_k1/th/harness.sv

- $K1_SOC_ROOT/verf/bt/bt_k1/tc/tc_base.sv

最后发现是通配符的问题,导致后面的文件都识别不了。

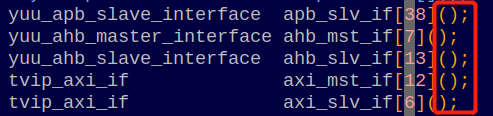

indentifer not in port list

原因是interface例化时最后没加()

Error-[UTOPN] Unknown type or port name

The type name 'SOC_TOP' is unknown, or the identifier 'dut' has not been

listed as a port, or the declaration might represent an instance missing

parentheses.

"../th/dut_inst.sv", 13

Source info: SOC_TOP dut;

原因模块例化时没加()

改成SOC_TOP dut();即可

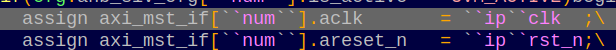

variable input ports cannot be driven

原因是vip的接口时钟复位是以参数的形式传入的,不能用assign来连接

Error-[TCF-CETE] Cannot evaluate the expression

完整报错:

- Error-[TCF-CETE] Cannot evaluate the expression

- ../env/k1_scb.sv, 251

- "(this.cfg.axi_mst_cfg.size + (~1'sd0))"

- Cannot evaluate the expression in right dimension bound.

- The expression must be compile time constant.

完整报错:

- Error-[TCF-CETE] Cannot evaluate the expression

- ../env/k1_scb.sv, 251

- "(this.cfg.axi_mst_cfg.size + (~1'sd0))"

- Cannot evaluate the expression in right dimension bound.

- The expression must be compile time constant.

原因是运行阶段队列右边大小不能确定

按如下修改即可:

Error-[IAP] Illegal assignment pattern

二维数组赋值错误:

删除二维数组后的标号:

找不到config变量

传入的变量在0,1跳变

一开始忘记写int了,直接input i。默认是1bit,数据只剩一位也就是0和1.

当fork-join/none遇上for循环:fork_for

遇到这么一个问题:

因为在for循环中启动fork进程时,当前循环会立刻结束,进入到下一个循环,因此在所有循环体中的i变量都会等于最后一次循环i的值。

解决办法如下:

https://zhuanlan.zhihu.com/p/553466412

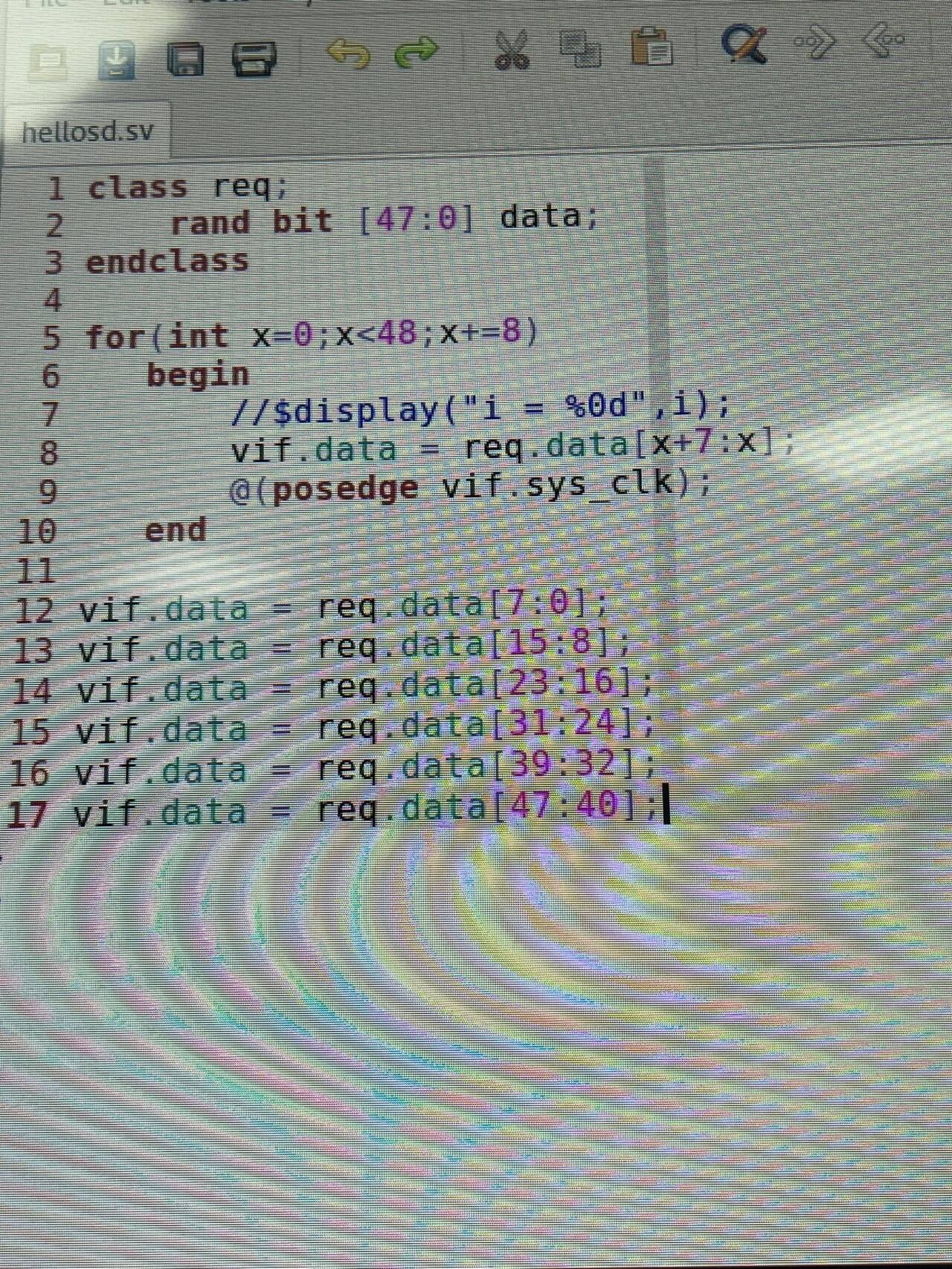

illegal range in part select

Q:无法使用for循环来分段取值, 但是下面这段这么赋值就没问题A:Verilog取值区间不能两端都是变量,改成下面形式即可—— req.data[x +: 8];

-

相关阅读:

数组元素替换位置

基于Qt的yolov5工程

RocketMQ整体架构及NameServer源码分析

解决:PicGo插件安装失败,失败码为1(404)

互联网摸鱼日报(2023-11-08)

TCP/UDP协议传输

apache配置https证书问题记录

1-1 开源许可证GPL, BSD, MIT, Mozilla, Apache, LGPL的介绍

HTML总结

2022最新前端vue面试题

- 原文地址:https://blog.csdn.net/weixin_51982763/article/details/139990671