-

指令系统、流水线

指令系统

分类

寻址方式

设计

能够改变控制流的指令:分支、跳转、过程调用、过程返回

操作码设计

MIPS

流水线

MIPS流水线

改进后

取指(IF)

译码(ID)

执行(EX)

存储器访问

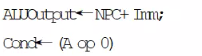

寄存器-寄存器 ALU

寄存器-立即值 ALU

分支

访存(MEM)

Load/Store

分支

写回(WB)

性能分析

吞吐率(TP)

单位时间流水线完成的任务数或输出的结果数

实际吞吐率

效率

相关

结构相关

某些指令组合在流水线中重叠执行时,产生资源冲突

解决方案:指令和数据分离;添加“气泡”

数据相关

指令在流水线中重叠执行时,流水线可能改变指令读/写的顺序,使得读/写的操作顺序不同于非流水线的实现顺序

分类

- 写后读相关(RAW)

- 写后写相关(WAW)

- 读后写相关(WAR)

定向技术(旁路/短路)

流水线锁

插入暂停周期

流水线调度(指令调度)

编译器重新组织代码顺序消除暂停

控制相关

分支指令带来的暂停

减少流水线处理分支指令时的暂停时钟周期数有如下两种途径:

- 在流水线中尽早地判断出分支转移是否成功。

- 尽早地计算出分支转移成功时的PC值(即分支的日标地址)。

延迟分支

向量处理机

向量处理方式

- 水平处理方式

- 垂直处理方式

- 分组处理方式

指令级并行

循环展开调度

展开循环体若干次,将循环级并行性转化为指令级并行

相关性

数据相关

名相关

名:指令使用的寄存器或存储器

名相关:两条指令使用相同的名,但之间并没有数据流- 反相关:WAR

- 输出相关:WAW

换名技术

控制相关

分支指令引起

动态调度

为了允许乱序执行,将基本流水线的译码阶段再分为以下两个阶段

- 流出(Issue,IS):指令译码,检查是否存在结构阻塞

- 读操作数(Read Operands,RO):当没有数据相关引发的阻塞时就读操作数

记分牌

所有的指令在流出(IS)阶段是顺序的,但是在第二阶段读操作数(RO)时,只要指令运行所需的资源满足并且没有数据阻塞,就应该允许指令乱序执行。

指令的执行过程

- 流出(IS)

- 读操作数(RO)

- 执行(EX)

- 写结果(WR)

记分牌需要记录的信息

Tolasulo算法

允许在指令由于存在相关而导致阻塞的情况继续执行,结合记分牌的关键和寄存器换名技术。寄存器换名通过保留站实现,保存等待流出和正在流出指令所需的操作数

与记分牌的差别

- 指令流出逻辑和保留站相结合实现寄存器换名,从而完全消除了数据写后写和先读后写相关这类名相关。

- 冲突检测和指令执行控制机制分开。一个功能部件的指令何时开始执行,由该功能部件的保留站控制,而记分牌则是集中控制。

- 计算的结果通过相关专用通路直接从功能部件进入对应的保留站进行缓冲,而不一定是写到寄存器。这个相关专用通路通过公共数据总线(CDB)实现。

指令的执行过程

- 流出(IS)

- 执行(EX)

- 写结果(WR)

控制相关的动态解决技术

分支预测缓冲

最简单的动态分支预测技术叫做分支预测缓冲技术(Branch Prediction Buffer或者Branch History Table,BTB或者BHT),它仅仅使用一片存储区域,记录最近一次或几次分支特征的历史。包括分支预测和预测位修改两个步骤。

分支目标缓冲

分支目标缓冲区(BTB)

- 第一栏存储分支转移成功的指令地址,当前指令地址与之比较

- 第二栏存储分支目标PC的值,将作为下一指令的地址送往PC寄存器

基于硬件的前瞻执行

允许在处理器判断指令是否能够执行之前就提前执行,以克服控制相关

关键思想:允许乱序执行,但必须顺序确认

再定序缓存(ROB):保存执行完毕但未经确认的指令及其结果,在前瞻执行的指令之间传递结果

指令的执行过程

- 流出(IS)

- 执行(EX)

- 写结果(WR)

- 确认

多指令流出技术

静态超标量技术

每个时钟周期流出的指令数目不定

动态多指令流出技术

超长指令字技术

将多条指令的操作组装为固定格式的指令包,形成一条非常长的指令

-

相关阅读:

手把手教你深度学习和实战-----全连接神经网络

Mac电脑配置Java环境和android环境,删除谷歌浏览器的自动更新

activemq学习笔记

代码随想录算法训练营第九天|二叉树(截止到合并二叉树)

【Linux】线程互斥

【UniApp】-uni-app-全局数据和局部数据

国家商用密码算法-SM4Tool.jar

【LeetCode刷题(数据结构)】:另一颗树的子树

TI/德州仪器 TPS2051CDBVR 功率电子开关

数据库的隔离级别

- 原文地址:https://blog.csdn.net/weixin_65199878/article/details/134516642