-

中断控制系统

1.NVIC全称为Nested Vectored Interrupt Controller,是Cortex-M处理器中的中断控制器。它用于管理外部和内部中断,并按照一定的优先级处理和响应中断请求。在Cortex-M处理器中,NVIC是实现优先级中断的关键组件之一。

2.MPU:内存管理单元。

3.

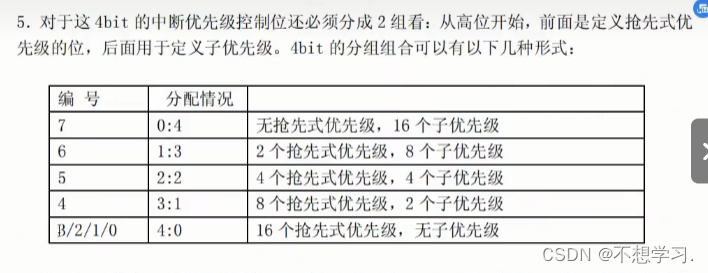

调试内核,可以控制内核进行暂停和运行。

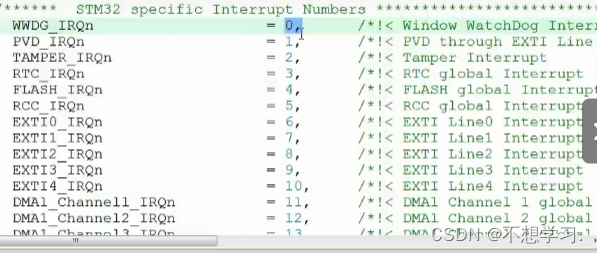

调试内核,可以控制内核进行暂停和运行。4.中断函数:是由外部事件,或者硬件调用的。不同的外设有不同的中断,对应不同的位。

这个图上面的中断,从上到下,优先级依次降低,当好几个中断事件同时发生的时候,先执行中断级高的中断。

中断还能嵌套,多个中断运行。

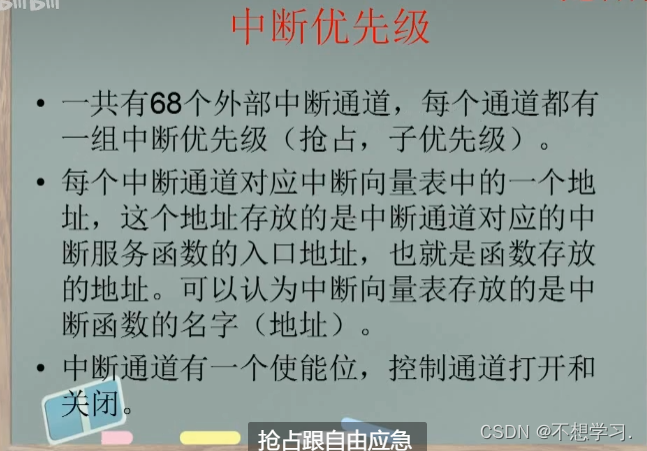

中断有抢占优先级和响应优先级两个。

中断通道有一个使能位,控制着通道打开和关闭。

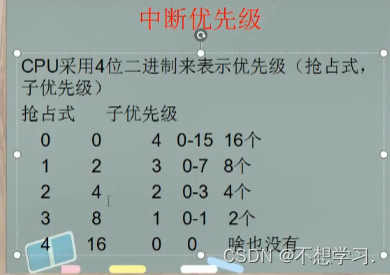

单片机的中断分为抢占优先级和响应优先级(子优先级),中断时首先由抢占优先级决定产生哪个中断。

抢占优先级的级别高于响应优先级。而数值越小所代表的优先级就越高。

高的抢占式优先级可以打断低的抢占式优先级,故名抢占;而在抢占式优先级相同的情况下,响应优先级越高,同时发生则先响应它,但是不能打断低响应优先级,响应表达的是响应速度。

在解释一下这里的两点:第一,如果两个中断的抢占优先级和响应优先级都是一样的话,则看哪个中断先发生就先执行;第二,高优先级的抢占优先级是可以打断正在进行的低抢占优先级中断的。而抢占优先级相同的中断,高优先级的响应优先级不可以打断低响应优先级的中断。

结合实例说明一下:假定设置中断优先级组为 2,然后设置中断 3(RTC_WKUP 中断)的抢占优先级为 2,响应优先级为 1。中断 6(外部中断 0)的抢占优先级为 3,响应优先级为 0。中断 7(外部中断 1)的抢占优先级为 2,响应优先级为 0。那么这 3 个中断的优先级顺序为:中断 7>中断 3>中断 6。

5.异常;是来自于CPU内部的。

-

相关阅读:

【DSP】【第四篇】如何生成bin和dat文件

2023年华为杯研究生数学建模竞赛辅导

ROS编译 调用第三方动态库(xxx.so)

【前端每日基础】day43——同步异步

stm32——hal库学习笔记(外部中断)

做百度百科需要什么资料,怎么创建产品类百度百科词条

java 获取格林威治时间(GMT) 时区 0时区 东八区【全网最详细】

AI安全入门-人工智能数据与模型安全

sqlyog导入csv失败的解决方法

C++入门_通讯录管理系统demo

- 原文地址:https://blog.csdn.net/qq_53909405/article/details/132618691