-

「Verilog学习笔记」使用8线-3线优先编码器Ⅰ实现16线-4线优先编码器

专栏前言

本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网

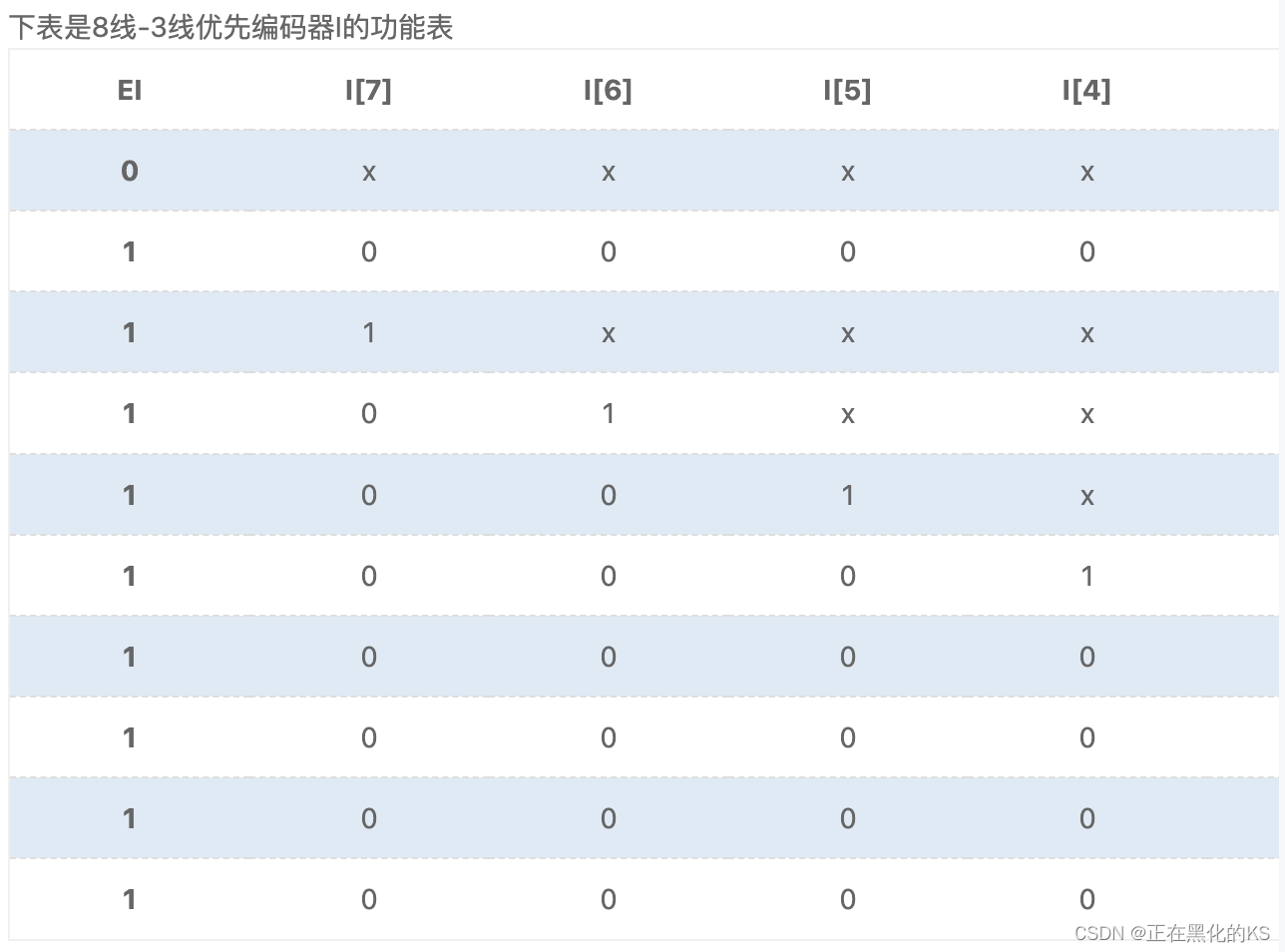

分析

当EI1=0时、U1禁止编码,其输出端Y为000,GS1、EO1均为0。同时EO1使EI0=0,U0也禁止编码,其输出端及GS0、EO0均为0。由电路图可知GS=GS1+GS0=0,表示此时电路输出端的代码L=0000是非编码输出。

当EI=1时,U1允许编码,若A[15:8]均无有效电平输人,则EO1=1,使EI0=1,从而允许U0编码,因此U1的优先级高于U0。

此时A[15:8]没有有效电平输入,U1的输出均为0。使4个或门都打开,L[2:0]取决于U0的输出,而L[3]=GS1总是等于0,所以输出代码在0000-0111之间变化。若只有A[0]有高电平输入,输出为0000,若A[7]及其他输入同时有高电平输人,则输出为0111。A[0]的优先级别最低。

当EI1=1且A[15:8]中至少有一个为高电平输人时,EO1=0,使EI0=0,U0禁止编码,此时L[3]=GS1=1,L[2:0]取决于U1的输出,输出代码在1000~1111之间变化,并且A的优先级别最高。

- `timescale 1ns/1ns

- module encoder_83(

- input [7:0] I ,

- input EI ,

- output wire [2:0] Y ,

- output wire GS ,

- output wire EO

- );

- assign Y[2] = EI & (I[7] | I[6] | I[5] | I[4]);

- assign Y[1] = EI & (I[7] | I[6] | ~I[5]&~I[4]&I[3] | ~I[5]&~I[4]&I[2]);

- assign Y[0] = EI & (I[7] | ~I[6]&I[5] | ~I[6]&~I[4]&I[3] | ~I[6]&~I[4]&~I[2]&I[1]);

- assign EO = EI&~I[7]&~I[6]&~I[5]&~I[4]&~I[3]&~I[2]&~I[1]&~I[0];

- assign GS = EI&(I[7] | I[6] | I[5] | I[4] | I[3] | I[2] | I[1] | I[0]);

- //assign GS = EI&(| I);

- endmodule

- module encoder_164(

- input [15:0] A ,

- input EI ,

- output wire [3:0] L ,

- output wire GS ,

- output wire EO

- );

- wire EO1 ;

- wire [2:0] Y0 ;

- wire [2:0] Y1 ;

- wire GS0, GS1 ;

- encoder_83 U0(

- .I (A[7:0]),

- .EI (EO1) ,

- .Y (Y0) ,

- .GS (GS0) ,

- .EO (EO)

- );

- encoder_83 U1(

- .I (A[15:8]),

- .EI (EI) ,

- .Y (Y1) ,

- .GS (GS1) ,

- .EO (EO1)

- );

- assign L[3] = GS1 ;

- assign L[2] = Y1[2] | Y0[2] ;

- assign L[1] = Y1[1] | Y0[1] ;

- assign L[0] = Y1[0] | Y0[0] ;

- assign GS = GS1 | GS0 ;

- endmodule

-

相关阅读:

【Python】sort 排序

LVS-DR模式+keepalived+nginx+tomcat实现动静分离、负载均衡、高可用实验

黑马程序员微服务 分布式搜索引擎3

从零开始,快速掌握创建百度百科技巧

ExtJS 教程汇总

FastReport .NET 2023.3.10 Crack

【Java SE】抽象类和接口

Git的下载安装和启动(win10)

累加和为 K 的最长子数组问题

前端的Docker入门终极指南

- 原文地址:https://blog.csdn.net/m0_54689021/article/details/134438873