-

JTAG 详解

10.1 JTAG简介

JTAG接口的基本工作原理是:在芯片内部定义一个TAP(Test Access Port,测试访问端口),开发人员使用连接到芯片的JTAG外部接口上的JTAG调试器,通过访问芯片内部的TAP端口来扫描芯片内部各个扫描单元以写 入或读取扫描寄存器的状态,从而对芯片进行测试和调试。一个扫描单元对应一个外部管脚,每个外部管脚有一个扫描寄存器BSR单元,所有这些管脚的扫描寄存 器连在一起就形成了扫描链。简单地说,PC通过JTAG调试器对目标板的调试就是通过TAP端口完成对扫描寄存器BSR和指令寄存器IR的读写访问。要了 解关于JTAG 更全面的知识,请参阅 IEEE1149.1标准。

JTAG接口的结构和时序分析

10.1.1 一些基本概念

JTAG

是Joint Test Action Group(联合测试行动组)的缩写,是一种国际标准测试协议,它遵守IEEE 1149.1标准。一个含有JTAG接口的处理器,只要时钟正常,就可以通过JTAG接口访问处理器的内部寄存器、挂在处理器总线上的设备以及内置模块的 寄存器。

TAP

是Test Access Port(测试访问端口)的缩写,是芯片内部一个通用的端口,通过TAP可以访问芯片提供的所有数据寄存器(DR)和指令寄存器(IR),对整个TAP的控制是通过TAP控制器(TAP Controller)完成的。

边界扫描

英文叫Boundary Scan,边界扫描的基本思想是在靠近芯片的输入输出管脚(PIN)上设置一个移位寄存器单元,也就是边界扫描寄存器(Boundary-Scan Register)。当芯片处于调试状态时,边界扫描寄存器可以将芯片和外部输入输出管脚隔离开来,通过边界扫描寄存器单元,可以实现对芯片外部输入输出 管脚的观察和控制。对于芯片的输出管脚可以通过与之相连的边界扫描寄存器单元把信号(数据)加载到该引脚中去,对于芯片的输入管脚,也可以通过与之相连的 边界扫描寄存器"捕获"该管脚上的输出信号。在正常的运行状态下,边界扫描寄存器对芯片来说是透明的,所以正常的运行不会受到任何影响,这样,边界扫描寄 存器提供了一种便捷的途径用于观测和控制所需调试的芯片。另外,芯片管脚上的边界扫描(移位)寄存器单元可以相互连接起来,使芯片的周围形成一个边界扫描 链(Boundary-Scan Chain),边界扫描链可以串行地输入和输出,通过相应的时钟信号和控制信号,就可以方便地观察和控制处在调试状态下的芯片。

10.1.2 JTAG接口信号

标准的JTAG接口定义了以下一些信号管脚:

TMS:测试模式选择信号,输入,IEEE 1149.1标准强制要求。

TCK:测试时钟信号,输入,IEEE 1149.1标准强制要求。

TDI:测试数据输入信号,输入,IEEE 1149.1标准强制要求。

TDO:测试数据输出信号,输出,IEEE 1149.1标准强制要求。

TRST:内部TAP控制器复位信号,输入,IEEE 1149.1标准不强制要求,因为通过TMS也可以对TAP Controller进行复位。

STCK:时钟返回信号,IEEE 1149.1标准不强制要求。

DBGRQ:目标板上工作状态的控制信号,IEEE 1149.1标准不强制要求

10.1.3 TAP控制器的状态机

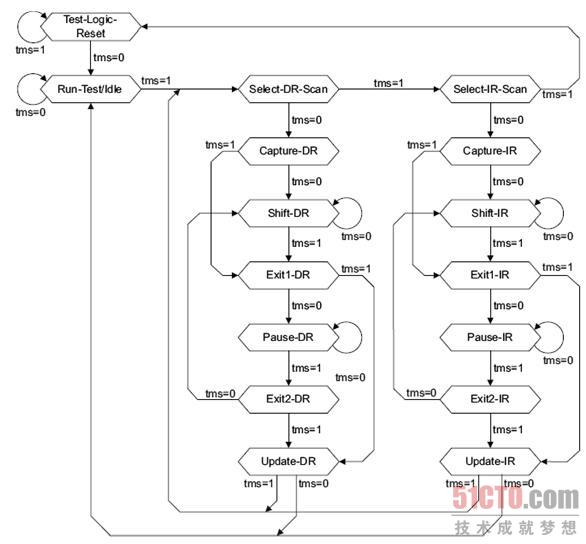

TAP控制器有16个同步状态,控制器的下一个状态TMS信号决定,TMS信号在TCK的上升沿被采样生效。

图10-1列出了TAP控制器的16个同步状态转换机制。

Test-Logic-Reset测试逻辑复位状态

处于这种状态下,测试逻辑被禁止以允许芯片正常操作,读IDCODE寄存器将禁止测试逻辑。

无论TAP控制器处于何种状态,只要将TMS信号在5个连续的TCK信号的上升沿保持高电平,TAP就将进入Test-Logic-Reset状 态,如果TMS信号一直为高电平,那么TAP将保持在Test-Logic-Reset状态,另外TRST信号也可以强迫TAP进入Test- Logic-Reset状态。

处于Test-Logic-Reset状态的TAP,如果下一个TCK的上升沿时TMS信号处于低电平,那么TAP将被切换到Run-Test-Idle状态。

Run-Test-Idle运行测试空闲状态

Run-Test-Idle是TAP控制器扫描操作空闲状态,如果TMS信号一直处于低电平,那么TAP将保持在TRun-Test-Idle状态。当TMS信号在TCK上升沿处于高电平,TAP控制器将进入Select-DR-Scan状态。

Select-DR-Scan选择数据寄存器扫描状态

Select-DR-Scan是TAP控制器的一个临时状态,边界扫描寄存器BSR保持它们先前的状态。

当TMS信号在下一个TCK上升沿处于低电平,TAP控制器进入Capture-DR状态,一个边界扫描寄存器的扫描操作同时被初始化。

如果TMS信号在下一个TCK上升沿处于高电平,TAP控制器将进入Select-IR-Scan状态。

Capture-DR捕获数据寄存器状态

如果TAP控制器处于Capture-DR状态,且当前指令是SAMPLE/PRELOAD指令,那么边界扫描寄存器BSR在TCK信号的上升沿捕 获输入管脚的数据。如果此时不是SAMPLE/PRELOAD指令,那么BSR保持它们先前的值,另外BSR的值被放入连接在TDI和TDO管脚之间的移 位寄存器中。

处于Capture-DR状态时,指令不会被改变。

如果TMS信号在下一个TCK上升沿处于高电平,TAP进入Exit1-DR状态。如果TMS信号在下一个TCK上升沿处于低电平,则TAP进入Shift-DR状态。

Shift-DR移位数据寄存器状态

在Shift-DR状态下,在每个TCK的上升沿,TDI-移位寄存器-TDO串行通道向右移一位,TDI的数据移入移位寄存器,移位寄存器最靠近TDO的位移到TDO管脚上。

处于Shift-DR状态时,指令不会被改变。

如果TMS信号在下一个TCK上升沿处于高电平,TAP进入Exit1-DR状态。如果TMS信号处于低电平,则TAP一直进行移位操作。

Exit1-DR退出数据寄存器状态1

Exit1-DR是TAP控制器的一个临时状态,如果TMS信号在下一个TCK上升沿处于高电平,TAP进入Update-DR状态;如果TMS信号在下一个TCK上升沿处于低电平,则TAP进入Pause-DR状态。

处于Exit1-DR状态时,指令不会被改变。

Pause-DR暂停数据寄存器状态

Pause-DR状态允许TAP控制器暂时停止TDI-移位寄存器-TDO串行通道的移位操作。

处于Pause-DR状态时,指令不会被改变。

如果TMS信号在下一个TCK上升沿处于高电平,TAP进入Exit2-DR状态;如果TMS信号处于低电平,则TAP一直保持暂停状态。

Exit2-DR退出数据寄存器状态2

Exit2-DR也是TAP控制器的临时状态,如果TMS信号在下一个TCK上升沿处于高电平,TAP进入Update-DR状态,结束扫描操作;如果TMS信号在下一个TCK上升沿处于低电平,则TAP重新进入Shift-DR状态。

处于Exit2-D状态时,指令不会被改变。

Update-DR更新数据寄存器状态

在正常情况下,边界扫描寄存器BSR的值是被锁存在并行输出管脚中,以免在EXTEST或SAMPLE/PRELOAD命令下执行移位操作时改变 BSR的值。当处于Update-DR状态时选择的是BSR寄存器,那么移位寄存器中的值将在TCK的下降沿被锁存到BSR寄存器的并行输出管脚中去。

处于Update-DR状态时,指令不会被改变。

如果TMS信号在下一个TCK上升沿处于高电平,TAP进入Select-DR-Scan状态;如果TMS信号在下一个TCK上升沿处于低电平,则TAP进入Run-Test-Idle状态。

Select-IR-Scan选择指令寄存器扫描状态

Select-IR-Scan是TAP控制器的一个临时状态。

如果TMS信号在下一个TCK上升沿处于低电平,TAP控制器进入Capture-IR状态,一个对指令寄存器的扫描操作同时被初始化。

如果TMS信号在下一个TCK上升沿处于高电平,TAP控制器将进入Test-Logic-Reset状态。

处于Select-IR-Scan状态时,指令不会被改变。

Capture-IR捕获指令寄存器状态

处于Capture-IR状态时,指令寄存器中的值被固定设置成0b0000001,并将它放入连接在TDI与TDO之间的移位寄存器中。

处于Capture-DR状态时,指令不会被改变。

如果TMS信号在下一个TCK上升沿处于高电平,TAP进入Exit1-IR状态;如果TMS信号在下一个TCK上升沿处于低电平,则TAP进入Shift-IR状态。

Shift-IR移位指令寄存器状态

在Shift-IR状态下,在每个TCK的上升沿,TDI-移位寄存器-TDO串行通道向右移一位,JTAG指令从TDI管脚上被逐位移入移位寄存器,而移位寄存器中的0b0000001则被逐位从TDO管脚移出。

处于Shift-IR状态时,指令不会被改变。

如果TMS信号在下一个TCK上升沿处于高电平,TAP进入Exit1-IR状态;如果TMS信号处于低电平,则TAP一直进行移位操作。

Exit1-IR退出指令寄存器状态1

Exit1-IR是TAP控制器的一个临时状态,如果TMS信号在下一个TCK上升沿处于高电平,TAP进入Update-IR状态;如果TMS信号在下一个TCK上升沿处于低电平,则TAP进入Pause-IR状态。

处于Exit1-IR状态时,指令不会被改变。

Pause-IR暂停指令寄存器状态

Pause-IR状态允许TAP控制器暂时停止TDI-移位寄存器-TDO串行通道的移位操作。

处于Pause-IR状态时,指令不会被改变。

如果TMS信号在下一个TCK上升沿处于高电平,TAP进入Exit2-IR状态;如果TMS信号处于低电平,则TAP一直处于暂停状态。

Exit2-IR退出指令寄存器状态2

Exit2-IR也是TAP控制器的临时状态,如果TMS信号在下一个TCK上升沿处于高电平,TAP进入Update-IR状态,结束扫描操作;如果TMS信号在下一个TCK上升沿处于低电平,则TAP重新进入Shift-IR状态。

处于Exit2-D状态时,指令不会被改变。

Update-IR更新指令寄存器状态

处于Update-IR状态时,移位寄存器中的值将在TCK的下降沿被锁存到指令寄存器中,一旦锁存成功,新的指令将成为当前的指令。

如果TMS信号在下一个TCK上升沿处于高电平,TAP进入Select-DR-Scan状态;如果TMS信号在下一个TCK上升沿处于电平,则TAP进入Run-Test-Idle状态。

10.1.4 JTAG接口指令集

JTAG接口指令集包含以下常用指令:

EXTEST指令

外部测试指令,必须全为0,TAP强制定义。该指令初始化外部电路测试,主要用于板级互连以及片外电路测试。

EXTEST指令在Shift-DR状态时将扫描寄存器BSR寄存器连接到TDI与TDO之间。在Capture-DR状态时,EXTEST指令将 输入管脚的状态在TCK的上升沿装入BSR中。EXTEST指令从不使用移入BSR中的输入锁存器中的数据,而是直接从管脚上捕获数据。在Update- DR状态时,EXTEST指令将锁存在并行输出寄存器单元中的数据在TCK的下降沿驱动到对应的输出管脚上去。

SAMPLE/PRELOAD指令

采样/预装载指令,TAP强制定义。在Capture-DR状态下,SAMPLE/PRELOAD指令提供一个从管脚到片上系统逻辑的数据流快照, 快照在TCK的上升沿提取。在Update-DR状态时,SAMPLE/PRELOAD指令将BSR寄存器单元中的数据锁存到并行输出寄存器单元中,然后 由EXTEST指令将锁存在并行输出寄存器单元中的数据在TCK的下降沿驱动到对应的输出管脚上去。

BYPASS指令

旁路指令,必须全为1,TAP强制定义。BYPASS指令通过在TDI和TDO之间放置一个1位的旁通寄存器,这样移位操作时只经过1位的旁通寄存 器而不是很多位(与管脚数量相当)的边界扫描寄存器BSR,从而使得对连接在同一JTAG链上主CPU之外的其他芯片进行测试时提高效率。

IDCODE指令

读取CPU ID号指令,TAP强制定义。该指令将处理器的ID号寄存器连接到TDI和TDO之间。

10.2 简易JTAG线缆原理

简易JTAG线缆一端连接到PC的并口,另一端连接到目标板的JTAG接口,PC并口中的数据、I/O管脚通过一个74XX244单向驱动芯片与目 标板JTAG口的TMS、TCK、TDI、TDO、TRST信号线相连,然后用PC上的软件来模拟JTAG所遵守的IEEE 1149.1标准协议,从而访问、控制目标板上处理器的I/O管脚状态,也就能访问、控制挂接在处理器总线上的flash芯片的I/O管脚,实现将数据写 入flash芯片中的功能。

-

相关阅读:

HDU 3549 Flow Problem【网络流入门题】

Python实验一

7.1.7 Java内部类

LeetCode每日一题(2310. Sum of Numbers With Units Digit K)

Python入门、环境搭建、变量、数据类型

密码算法、密钥体系---安全行业基础篇1

【进程VS容器VS虚拟机】

Modbus转Profinet网关接电表与工控机通讯

【2023研电赛】全国技术竞赛一等奖:基于FPGA的超低时延激光多媒体终端

编程(代码、软件)规范(适用嵌入式、单片机、上位机等)

- 原文地址:https://blog.csdn.net/lbaihao/article/details/134077231