-

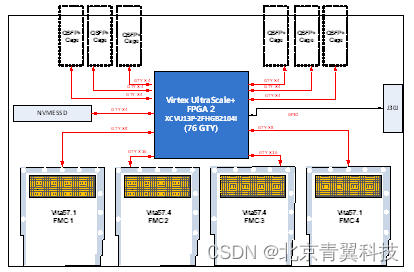

【TES641】基于VU13P FPGA的4路FMC接口基带信号处理平台

板卡概述

TES641是一款基于Virtex UltraScale+系列FPGA的高性能4路FMC接口基带信号处理平台,该平台采用1片Xilinx的Virtex UltraScale+系列FPGA XCVU13P作为信号实时处理单元,该板卡具有4个FMC子卡接口(其中有2个为FMC+接口),各个节点之间通过高速串行总线进行互联,该FPGA支持最大32Gbps的高速串行总线,适用于100G以太网、JESD204B/JESD204C等高速接口。板卡采用嵌入式非标结构,具有优良的抗振动设计、散热性能和独特的环境防护设计,适用于超带宽基带信号处理、多路AD/DA等同步采集处理等场景。

技术指标

1、Virtex UltraScale+系列 FPGA处理器:XCVU13P-2FHGB2104I;

2、 处理性能:

1) 逻辑资源:3780K Logic Cells;

2) DSP Slices:12288个;

3) GTY Transceivers:76个32.75Gbps;

1、 动态存储性能:

1) 动态存储数量:2组DDR4 SDRAM;

2) 动态存储容量:每组4GByte,每个颗粒为8GBit;

3) 动态存储带宽:工作时钟1000MHz,数据率2000Mbps;

2、 互联性能:

1) FPGA与FMC1:GTY x8@32Gbps/lane;

2) FPGA与FMC2:GTY x8@32Gbps/lane;

3) FPGA与FMC3:GTY x16@32Gbps/lane;

4) FPGA与FMC4:GTY x16@32Gbps/lane;

5) FPGA与光纤:6个GTY Quard@32Gbps/lane;

6) FPGA与NVME:x4 GTY@32Gbps/lane;

7) FPGA与J30J:10路GPIO

3、 物理与电气特征

1) 板卡尺寸:255 * 290mm

2) 板卡供电:6A max@+12V(±5%)

3) 散热方式:金属导冷+风冷散热

4、 环境特征

1) 工作温度:-40°~﹢85°C,

2) 存储温度:-55°~﹢125°C;

3) 工作湿度:5%~95%,非凝结

软件支持

1、 可选集成板级软件开发包(BSP):

1) DSP底层接口驱动;

2) FPGA底层接口驱动;

3) 板级互联接口驱动;

4) 基于FMC AD/DA子卡的底层驱动;

2、可根据客户需求提供定制化算法与系统集成:

应用范围

1、软件无线电;

2、雷达与基带信号处理

-

相关阅读:

linux运维基础2

内存管理:判断对象是否存活

1. 算法简介

亚马逊云科技顾凡解读云计算助力初创快速抢滩生成式AI新风口

6G安全通信指标

C/C++ 代码中使用 CMake 工程目录

智能家居—ESP32开发环境搭建

python3.6环境下安装gevent,附协程TCP服务器客户端代码

【sizeof()的使用方式】简洁明了初识C语言

凌恩客户文献|宏基因组binning解析中国浓味白酒窖泥微生物群落MAGs和代谢潜力

- 原文地址:https://blog.csdn.net/beijingqingyikeji/article/details/134005570