-

数字IC基础协议篇(1)——I2C协议

写在前面的话

协议介绍:

I2C(Inter-Integrated Circuit)是一种常用的串行通信协议,用于连接在数字系统中的多个集成电路。它是由飞利浦公司(Philips)于上世纪80年代开发的,并在现在被广泛应用于各种电子设备和嵌入式系统中。I2C协议使用两根线进行通信:SDA(Serial Data Line)和SCL(Serial Clock Line)。SDA是用于传输数据的双向线路,而SCL是一个时钟线路,用于同步数据的传输。这两根线路都需要外部上拉电阻来恢复默认高电平状态。

在I2C通信中,每个设备都有唯一的地址,可以作为主设备(Master)或从设备(Slave)进行工作。主设备负责发起通信并控制总线的操作,而从设备则根据主设备的命令进行响应。

数据传输过程中,主设备发起开始信号(Start)和停止信号(Stop),用于标识通信的开始和结束。开始信号指示着总线空闲状态结束,而停止信号表示着通信的终点。在通信过程中,主设备通过发送地址和数据来与从设备进行通信。从设备根据地址来判断是否需要响应,并通过数据线回复数据。

I2C协议支持不同的数据传输速率,最常见的是标准模式(100 kHz)和快速模式(400 kHz)。此外,还有更高速的Fast Mode Plus(1 MHz)和超高速模式(3.4 MHz)。

I2C协议仅使用两根线路、支持多主设备、可通过总线电源供电等。它被广泛应用于各种应用领域,包括传感器、存储器、显示屏、温度计、实时时钟等。重要性:

- 设备互联:I2C协议是一种常见的串行通信协议,广泛用于数字系统中的设备互联。了解和熟练应用I2C协议可以使工程师能够设计和连接各种集成电路(IC),传感器,存储器,显示屏等设备,构建复杂的系统。

- 系统集成:许多数字系统需要与多个设备进行通信,并且这些设备通常使用不同的通信协议。作为数字IC工程师,掌握I2C协议可以将不同设备集成到一个系统中,简化系统设计和布局。

- 资源共享:通过I2C总线,多个设备可以共享同一个总线来传输数据。这种资源共享机制可以显著降低系统成本和功耗。掌握I2C协议可以使工程师能够实现设备之间的数据共享和通信,提高系统的效率和性能。

- 系统调试和故障排除:在开发和调试数字系统时,I2C协议的理解和熟练使用对于故障排除和调试是至关重要的。通过监视和分析I2C通信,工程师可以定位问题并解决通信故障,确保系统的正常运行。

- 设备驱动程序开发:在嵌入式系统中,往往需要编写设备驱动程序来与从设备进行通信。掌握I2C协议可以帮助工程师编写高效可靠的设备驱动程序,实现与各种从设备的数据交换和控制。

对于找工作的帮助:

- 简单易学:相对于其他复杂的通信协议,如SPI、CAN等,I2C协议相对简单。它只需要理解两根线路(时钟线和数据线)以及基本的传输格式就可以开始使用。因此,对于初学者来说,I2C协议是较为容易上手的。

- 常见应用广泛:I2C协议在各种应用中都有广泛的应用,例如嵌入式系统、传感器网络、数字IC设计等领域。了解I2C协议可以帮助初学者更好地理解和应用实际项目中的通信需求。

- 开发资源丰富:针对I2C协议的开发资源(如文档、示例代码、软件库等)非常丰富。许多厂商提供了针对I2C的硬件产品和相关支持,以及开源社区也有很多关于I2C协议的开发资源。初学者能够更轻松地获取学习资料和实践经验。

- 实验成本低:使用I2C协议进行实验的成本相对较低。大多数I2C设备价格较为合理,而且可以通过一些常见的开发板和模块来快速构建实验环境。这使得初学者能够以较低的成本进行实际的通信测试和项目开发。

- 高度可扩展:尽管I2C协议本身相对简单,但它具有高度可扩展性。初学者可以通过学习I2C协议的基础知识,进一步了解如何应用其他高级功能和特性,例如多主机模式、时序控制、高速模式等。有助于逐步提升技能水平。

I2C协议应用框图

I2C协议应用框图如下:

1)只需要两条总线线路:一条串行数据线(SDA)和一条串行时钟线(SCL)。

2)连接到总线上的每个设备都可通过唯一地址进行软件寻址,并且在任何时候都存在简单的主/从关系;主设备可作为主发送器或主接收器运行

3)这是一条真正的多主总线,包括碰撞检测和仲裁,以防止两个或多个主设备同时启动数据传输时出现数据损坏。

4)串行、面向 8 位的双向数据传输,在标准模式下传输速率最高可达 100 kbit/s,在标准模式下传输速率最高可达 400 kbit/s。在标准模式下最高可达 100 kbit/s,在快速模式下最高可达 400 kbit/s,在高速模式下最高可达 3.4 Mbit/s。

5)串行、8 位定向、单向数据传输,在超高速模式下最高可达 5 Mbit/s

6)片上滤波可拒绝总线数据线上的尖峰,以保持数据的完整性。

7)可连接到同一总线的集成电路数量仅受最大总线电容(默认是400pF)的限制。在某些情况下,可能允许更大的电容。I2C协议经典应用框图

I2C总线负载电容

总线负载电容推荐值不超过400pf,超过Spec时需要设置Buffer进行隔离。

I2C数据格式

I2C协议的数据格式包括以下几个部分:开始信号、设备地址、寄存器地址(可选)、数据、应答位和停止信号。通过这种格式,主设备和从设备能够按照约定的规则进行数据的传输和解析,实现可靠的通信。

-

I2C协议使用了一种特定的数据格式来进行通信。在传输过程中,数据被分为字节(Byte)单位,并按照特定的格式进行传输和解析。

-

每一个字节都有8位(Bit),通信的起始由主设备(Master)发出开始信号(Start)来表示。接下来的第一个字节是设备地址(Address),它用于指示要通信的从设备(Slave)的身份。地址由7位组成,最高位用于表示读取(1)或写入(0)操作。

-

在设备地址之后,可能会跟着一个可选的寄存器地址(Register

Address)。这个寄存器地址用于指定从设备内部的特定寄存器,以便进行读取或写入操作。寄存器地址也是一个字节大小。 -

在寄存器地址之后,可以发送多个字节的数据。这些数据可以是要写入寄存器的值,或者是从设备读取到的数据。在写入操作中,主设备将数据逐个字节地发送给从设备。而在读取操作中,主设备发送读取请求后,从设备会按照顺序将数据逐个字节地回复给主设备。

-

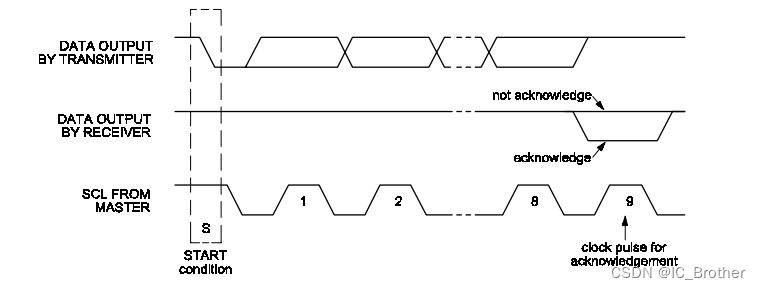

在每个字节的传输之间,都会有一个应答位(ACK)来确认数据的接收情况。当从设备成功接收到一个字节时,它会发送一个应答位来通知主设备继续发送下一个字节。而如果从设备未能成功接收到一个字节,它会发送一个非应答位(NACK)来终止数据传输。

-

在通信的末尾,主设备会发送停止信号(Stop),表示通信结束。

协议注意点

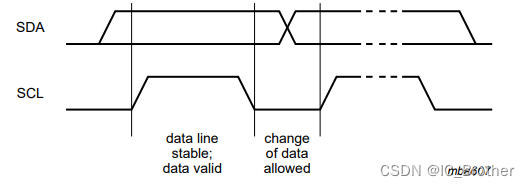

1. 数据有效性:

SDA线上的数据在时钟的HIGH周期内必须稳定。当SCL线上的时钟信号为LOW时,数据线的LOW状态才能改变。每个数据位对应一个时钟脉冲。

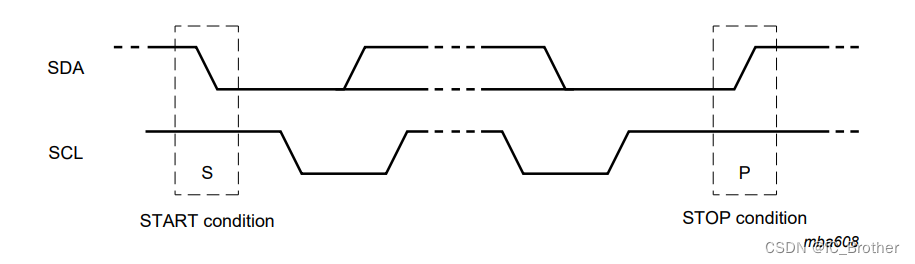

2. 起始和终止条件:起始条件:当 SCL 为高电平时,SDA 由高电平转换为低电平。

终止条件:当 SCL 为高电平时,SDA 从低电平转换为高电平。

3. 数据格式:

SDA 传输的字节长度为 8 位。每次传输的字节数不受限制。每个字节后必须有一个应答位,数据传送时,先传送最高位(MSB)。如果从机要完成一些其他功能后,例如一个内部中断服务程序,才能接收或发送下一个完整的数据字节。可以使时钟线 SCL 保持低电平迫使主机进入等待状态。 当从机准备好接收下一个数据字节并释放时钟线 SCL 后 数据传输继续

4. 应答位:

应答位的信号定义如下:主机在第9位传输期间,在SCL时钟脉冲期间释放 SDA 线(拉高SDA)。以便从机能将 SDA 线拉至低电平,并在该时钟脉冲期间保持稳定的低电平。

通常从机在接收到的每个字节后,除了用 CBUS 地址开头的报文,必须产生一个应答位。当从机不能响应从机地址时,从机必须使数据线保持高电平。主机之后产生一个停止条件终止传输或者产生重复起始条件开始新的传输。

产生非应答的几种情况:

- 总线上没有对应传输地址的从机,因此没有设备响应确认。

- 从机无法接收或发送,因为它正在执行某些实时 功能,尚未准备好开始与主机通信。

- 从机收到不理解的数据或命令。

- 从机无法接收更多数据字节。

- 主机接收器必须向从机发送器发出传输结束信号。

5. 时钟同步和仲裁

时钟同步:

多个主机可以同时开始在空闲的I2C总线上传输数据,因此必须有一种方法来决定由哪个主机控制总线并完成传输。这是通过时钟同步和仲裁实现的,单主角的系统中不需要时钟同步和仲裁。时钟同步通过线与连接 I2C 接口到 SCL 线来执行,这就是说 SCL 线的高到低切换会开始数低电平周期,而一旦器件的时钟变低电平,它会使 SCL 线保持这种状态直到时钟的高电平。

同步 SCL 时钟的低电平周期由时钟低电平周期最长的主机决定,而其高电平周期则由时钟高电平周期最短的主机决定。(SCL是线与连接的)仲裁:

只有当总线空闲时,主机才能开始传输。两个主机可在启动条件的最短保持时间 (tHD;STA) 内产生一个启动条件,从而在总线上产生一个有效的启动条件。这时需要进行仲裁,以确定由哪个主机完成传输。由于SDA也是线与连接的,所有主机会在SCL拉高时将自己产生的SDA信号与总线SDA信号进行对比,当检测到和总线不一致时,则退出仲裁,直到SDA总线上信号和该主机一致。

整个仲裁过程不会遗漏发送的SDA信息,仲裁时间的长短和SDA对应的信息正确与否相关,即仲裁所需时间是不确定的。也没有额外的仲裁单元,每个主机内部都会检查SDA总线和自己发送的SDA对应位的信息。

I2C读写EEPROM例程(基于iverilog和gtkwave)

难度:⭐⭐

推荐度:⭐⭐⭐

推荐天数:1~3天软件环境要求

要求的软件和EDA环境:

(1)操作系统要求:

Windows

(2)EDA 软件要求:

iverilog & gtkwave项目学习目的:

(1)熟练掌握I2C协议;

(2)熟悉 Verilog HDL仿真;

(3)熟练掌握EEPROM;

(4)掌握iverilog和gtkwave联合仿真的流程和脚本。项目框图

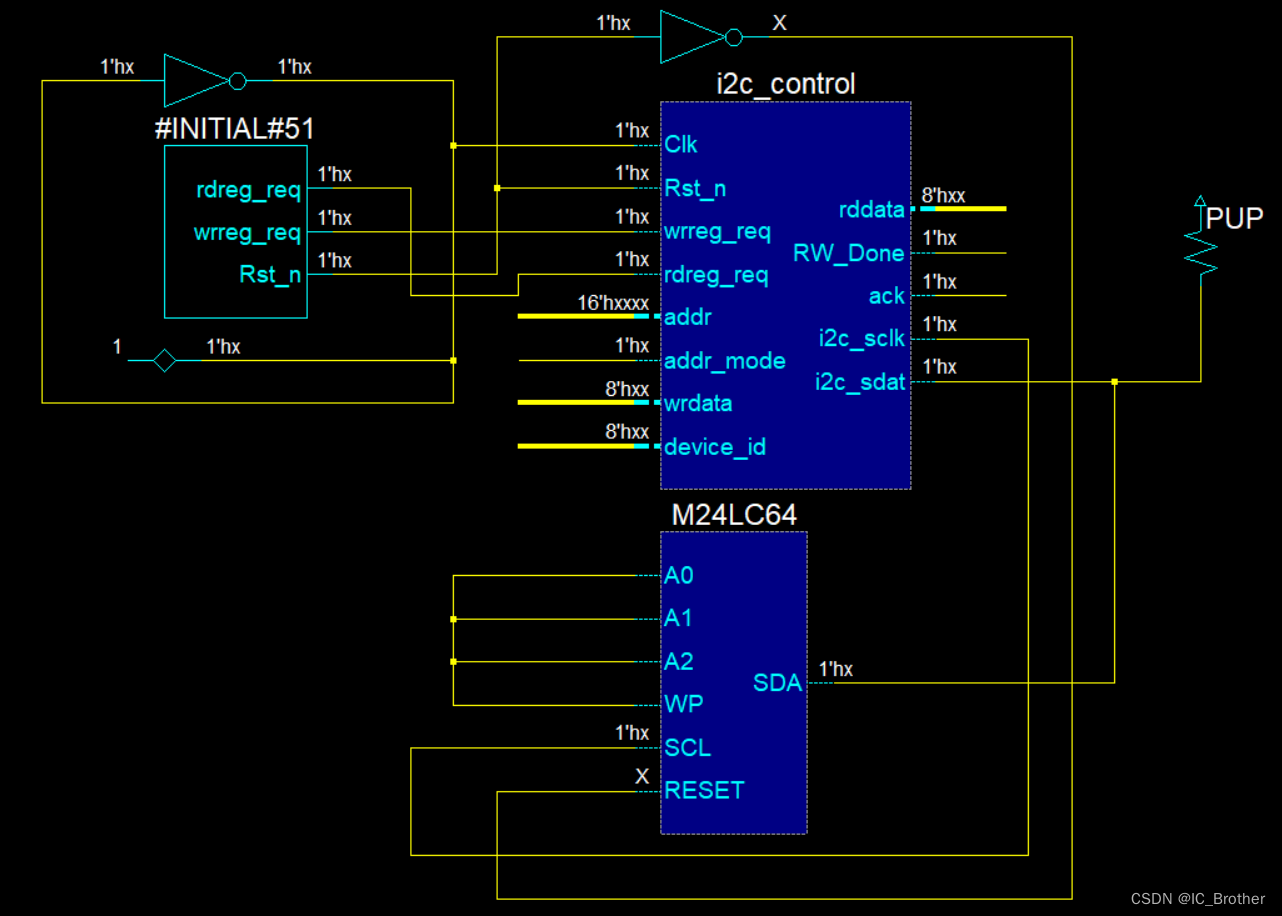

整体项目包含两部分,一个是I2C协议的控制模块,另一个是EEPROM模块(M24LC64),在SDA端口上配置一个上拉电阻。

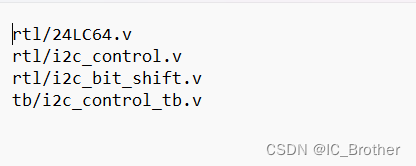

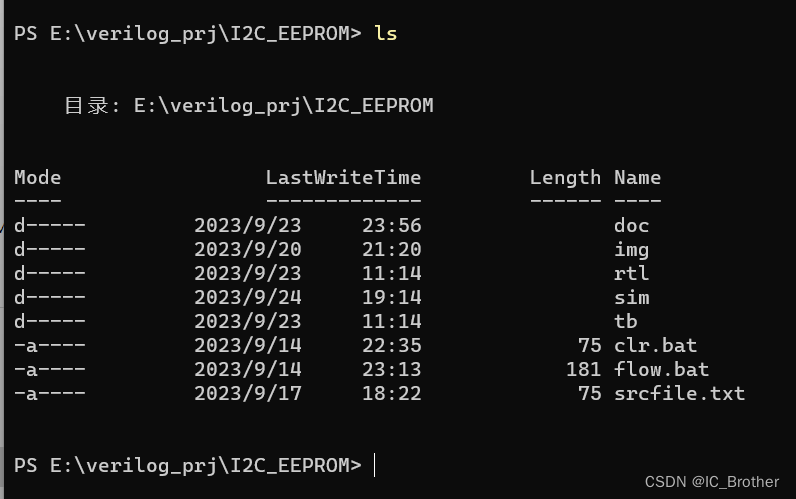

项目工程文件如下:

1、rtl和tb文件夹分别为设计文件和仿真文件;

2、srcfile.txt 是仿真文件及对应的路径;

3、flow.bat是仿真脚本,进终端运行这个就可以dump出波形并调用gtkwave查看;

4、clr.bat是清除脚本,用于删除仿真的波形数据。

项目代码:

本项目采用的是iverilog和gtkwave完成前仿,利用bat脚本完成,首先将设计文件和仿真tb文件的路径和名称保存至txt文件中,文件内容如下:

文件名为“srcfile.txt”

bat脚本:### clr.bat begin ### echo "clean the simulation files " del wave del wave.lxt echo "Finished" ### clr.bat end ### #### flow.bat begin #### echo "Compile Start" iverilog -o wave -c srcfile.txt echo "Compilation completed" vvp -n wave -lxt2 echo "Generating Waveform Files" echo "Open Waveform File" gtkwave wave.lxt #### flow.bat end ####- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

tb文件加入dump波形的代码段:

iverilog和gtkwave仿真时需要在tb文件中加入以下代码:initial begin $dumpfile("wave.lxt"); $dumpvars(0, i2c_control_tb); // dump所有信号波形 end- 1

- 2

- 3

- 4

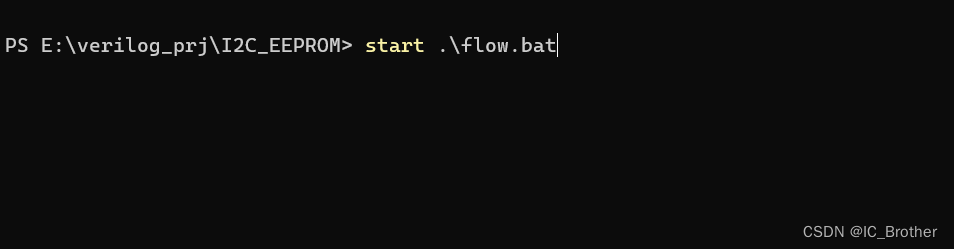

仿真流程:

1、cd到对应的项目文件夹中,查看脚本和对应文件

2、执行flow.bat脚本

3、脚本结果和波形查看

4、gtkwave查看对应波形:

EEPROM读写数据正常,I2C驱动正常。

5、附上芯片手册中的读写波形:

支持Byte写和随机读

总结

I2C协议是一种串行通信协议,用于在集成电路之间进行数据传输。它使用两根线路,即时钟线(SCL)和数据线(SDA),通过主从模式进行通信。关于I2C协议读写EEPROM的例程总结:

- 初始化I2C总线:首先,需要初始化I2C总线,配置相关的硬件参数,例如时钟频率、引脚配置等。这通常由硬件相关的库或函数提供。

- 设置EEPROM设备地址:确定要进行通信的EEPROM设备的地址。每个EEPROM设备都有一个唯一的地址,可以通过查看设备的规格说明书或数据手册来获取。

- 发送写命令和内存地址:如果要写入EEPROM,首先发送写命令(0xA0)到设备的地址。然后,发送要写入数据的内存地址。

- 发送数据:将要写入EEPROM的数据逐个字节地发送到设备。每发送一个字节,需要等待设备的响应确认。

- 停止条件:完成数据写入后,发送停止条件(Stop Condition),即在SCL为高电平时,SDA线由低电平转为高电平。

- 发送读命令和内存地址:如果要读取EEPROM,首先发送写命令(通常为0xA0)到设备的地址。然后,发送要读取数据的内存地址。

- 重复启动条件:再发送一个重复启动条件,即在SCL为高电平时,SDA线由高电平转为低电平。

- 发送读命令和设备地址:将读命令(0xA1)发送到设备的地址,指示要读取数据。

- 读取数据:通过I2C总线接收从EEPROM设备返回的数据。每接收一个字节,需要发送ACK信号表示继续接收,直到接收完所有需要的数据。

-

相关阅读:

Springboot旅游网站管理系统3ogg3计算机毕业设计-课程设计-期末作业-毕设程序代做

网络安全(黑客)自学

SDUT 2022 summer team contest 6th(for 21)

算法:(七)队列

Linux 系统监控与性能调优

系统与应用监控的缜密思路

数据分析 - 概率计算

这项最新的调查研究,揭开多云发展的两大秘密

枚举类 typede fmalloc 函数 free 函数 位运算

06 CSS03

- 原文地址:https://blog.csdn.net/HFUT90S/article/details/132951703