-

FPGA的DQPSK调制解调Verilog

名称:DQPSK调制解调

软件:Quartus

语言:Verilog

要求:

使用Verilog语言进行DQPSK调制和解调,并进行仿真

代码下载:DQPSK调制解调verilog,quartus_Verilog/VHDL资源下载

代码网:hdlcode.com

部分代码展示

//DPSK解调模块 module QPSK_demodu( input clk, input rst, input [7:0] qout,//调制波 input [7:0] cos_wave,//本地载波 input [7:0] sin_wave,//本地载波 output [1:0] data//解调输出 ); wire [16:0] cos_mul; wire [16:0] sin_mul; assign cos_mul=cos_wave*qout;//调制波形与本地载波相乘 assign sin_mul=sin_wave*qout;//调制波形与本地载波相乘 reg [5:0]filter_cos_cnt=0;//32 reg [5:0]filter_sin_cnt=0;//32 reg demodulate_a=0; reg demodulate_b=0; //采用计数器滤波,检测到cos_mul(15) = '1'后计数到25 always @(posedge clk) begin if(rst) filter_cos_cnt<=6'd0; else if(cos_mul[15]==1) filter_cos_cnt<=6'd1; else if(filter_cos_cnt==6'd0) filter_cos_cnt<=6'd0; else if(filter_cos_cnt>=6'd25) filter_cos_cnt<=6'd0; else filter_cos_cnt<=filter_cos_cnt+6'd1; end always @(posedge clk) begin if(filter_cos_cnt==6'd0) demodulate_a<=0;//滤波输出解调的a路信号 else demodulate_a<=1;//滤波输出解调的a路信号 end //采用计数器滤波,检测到sin_mul(15) = '1'后计数到25 always @(posedge clk) begin if(rst) filter_sin_cnt<=6'd0; else if(sin_mul[15]==1) filter_sin_cnt<=6'd1; else if(filter_sin_cnt==6'd0) filter_sin_cnt<=6'd0; else if(filter_sin_cnt>=6'd25) filter_sin_cnt<=6'd0; else filter_sin_cnt<=filter_sin_cnt+6'd1; end always @(posedge clk) begin if(filter_sin_cnt==6'd0) demodulate_b<=0;//滤波输出解调的b路信号 else demodulate_b<=1;//滤波输出解调的b路信号 end // reg [7:0] cnt=8'd0; always @(posedge clk) begin cnt<=cnt+1; end reg a_buf=0; reg b_buf=0; reg a_buf2=0; reg b_buf2=0; wire D_a,D_b; always@(posedge clk) if(cnt==8'd1) begin a_buf<=demodulate_a; b_buf<=demodulate_b; a_buf2<=a_buf;//a路延迟 b_buf2<=b_buf;//b路延迟 end //差分解调 assign D_a=a_buf ^ a_buf2;//Cn=Bn^Bn-1 assign D_b=b_buf ^ b_buf2;//Cn=Bn^Bn-1 wire [1:0]data_buf; assign data_buf={D_a,D_b};//输出差分解调后的2bit数据 assign data=data_buf; endmodule设计文档(文档点击可下载):

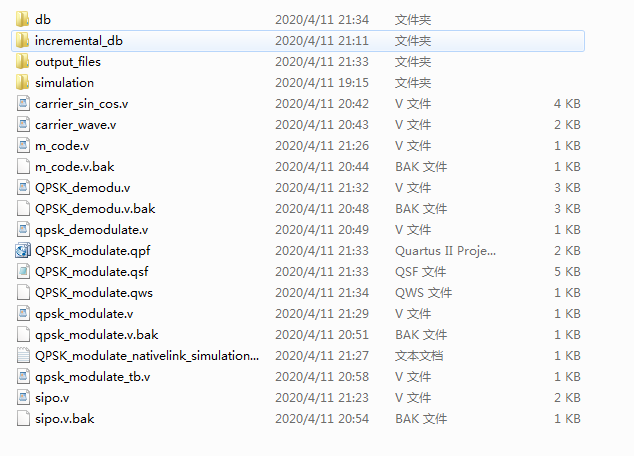

1. 工程文件

2. 程序文件

3. 程序编译

4. RTL图

5. Testbench

6. 仿真图

载波模块

调制模块

解调模块

-

相关阅读:

[附源码]计算机毕业设计springboot校园招聘微信小程序

一篇文章带你走进cookie,session,Token的世界

linux从入门到精通

期望+拆贡献+充斥:CF1349D

齐鲁大地市省学馆《乡村振兴战略下传统村落文化旅游设计》山东图书香

MQTT第二话 -- emqx高可用集群实现

PGL图学习之图神经网络ERNIESage、UniMP进阶模型[系列八]

PMP考试后多久出结果?(内附查成绩流程)

【自动化测试教程】Java+Selenium自动化测试环境搭建

ChatGPT API 学习

- 原文地址:https://blog.csdn.net/diaojiangxue/article/details/133253929