-

【文档+视频】Verdi基础教程

目录

8、如何查找位于不同层次的驱动信号【跨层次查看信号,看最终驱动谁,或者看最终被谁驱动】?【重点】

6、如何产生 partial hierarchy schematic?

2、如何查看状态的执行语句?[重点]3、如何查看状态的转移条件?

前言

通过此篇博客,能够了解到Verdi的环境配置、启动Verdi的方法、Verdi常用的操作方法。

配套教学视频介绍Verdi的基本使用方法

1.Verdi 环境配置

.bashrc中需配置三个路径

- VERDI_HOME / NOVAS_HOME: 其实就是Verdi的安装路径

- PATH : 在Verdi的安装路径中,Linux能找到启动Verdi的快捷键

- LD_LIBRARY_PATH : 让Verdi找到相应的库文件,从而进行相应的仿真

- export Verdi_HOME=$Synopsys_Dir/Verdi2015

- export PATH=$Verdi_HOME/bin:$PATH

- export LD_LIBRARY_PATH="/opt/Synopsys/Verdi2015/share/PLI/lib/linux64":$PATH

- export LD_LIBRARY_PATH="/opt/Synopsys/Verdi2015/share/PLI/VCS/linux64":$PATH

2.VCS 产生Verdi 波形

1、tb中加入相应的系统函数

如异步FIFO设计:

- initial begin

- $fsdbDumpfile("fifo.fsdb"); //fifo.fsdb是波形文件名字,根据设计名字自行定义。

- $fsdbDumpvars(0); //0代表dump电路设计所有层次; 若为1,则代表dump1层。

- end

在TB中要添加$stop或$finish,否则波形会一直dump下去。

2、makefile中加入相应的选项

- #************parameter input*************

- #※prepare the source list file and then make add the soucefile name

- #for example ,the Verilog source file's name is vlog_list.f then :make norsim src_list=file_list

- src_list = sim

- simv_name = simv

- vpdpluse_name = vcdpluse

- cov_file_name = coverage

- vdb_name = $(simv_name)

- #************constant command************

- #compile

- NOR_VCS = vcs -full64 -sverilog +v2k -timescale=1ns/1ns -debug_all +notimingcheck +nospecify +vcs+flush+all -o $(simv_name) -f $(src_list).f -l compile.log

- #coverage compile switch

- COV_SW = -cm line+cond+fsm+branch+tgl

- #verdi dump wave compile option

- VERDI_SW = -P /opt/Synopsys/Verdi2015/share/PLI/VCS/linux64/novas.tab \

- /opt/Synopsys/Verdi2015/share/PLI/VCS/linux64/pli.a

- #run option

- RUN_GUI = -R -gui -l run.log

- RUN_VPD = -R +vpdfile+$(vpdpluse_name).vpd -l run.log

- RUN_COV = -R $(COV_SW) -cm_name $(vdb_name) -cm_dir ./$(cov_file_name) -l run.log

- RUN_VER = -R +fsdb+autoflush -l run.log

- #************command************

- #normally sim

- norsim:

- $(NOR_VCS) $(RUN_GUI)

- #post-process

- postsim:

- $(NOR_VCS) $(RUN_VPD)

- dve -vpd $(vpdpluse_name).vpd

- #coverage

- covsim:

- $(NOR_VCS) $(COV_SW) $(RUN_COV)

- dve -covdir $(cov_file_name).vdb

- #verdi

- versim:

- $(NOR_VCS) $(VERDI_SW) $(RUN_VER)

- //****$(NOR_VCS) : 编译阶段—— 执行VCS普通编译过程,编译过程中产生simv.name文件;

- //****$(VERDI_SW): 在编译过程中添加verdi开关选项,主要加入novas.tab类表文件和 pli.a 接口文件文件;

- //****$(RUN_VER) : 仿真阶段—— 主要用来产生 .fsdb 文件

- verdi -sv -f $(src_list).f -ssf *.fsdb -nologo

- //****启动Verdi,并打开fsdb文件

- #rm

- clr:

- rm -rf *csrc ./*.daidir $(simv_name) *simv* DVE* ucli* *.vpd *.vdb *.log *.fsdb *novas* *.dat *Log *rc *conf

3.nTrace

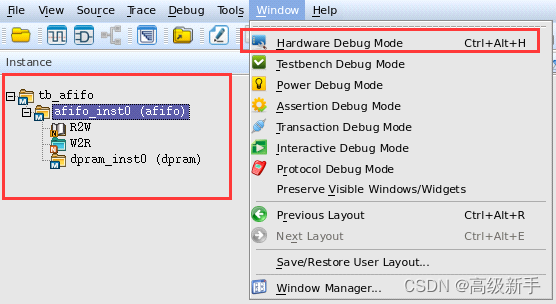

1、如何调用Verdi? 【重点】

- Verdi或verdi -nologo

- makefile中的命令

2、如何查看包含的设计架构?

3、如何查寻模块实例化的位置?【重点】

①在设计结构中双击实例化模块的名字 ->源代码窗口高亮了设计部分的模块名

②再双击高亮的模块名->看到在上层模块中的哪一行被调用了4、在nTrace中如何查找 模块和信号?【重点】

或Shift+A:

搜索通配符 *

5、如何查寻字符串?【重点】

类似于文本查找功能。

或者快捷键斜杠/:

6、如何查看某个信号是被哪些信号驱动的?【重点】

双击信号名,或者单击选中信号名然后点击:

接着可以通过快捷键N查看下一个被赋值/驱动的位置 或者快捷键P查看上一个被驱动/赋值的位

置。 或点击L后的上、下箭头来选择。7、如果查看某个信号驱动了哪些信号?【重点】

选中信号,然后点一下:

接着可以通过快捷键N查看下一个驱动其他信号的位置 或者快捷键P查看上一个驱动其他信号的

位置。或点击L后的上、下箭头来选择。8、如何查找位于不同层次的驱动信号【跨层次查看信号,看最终驱动谁,或者看最终被谁驱动】?【重点】

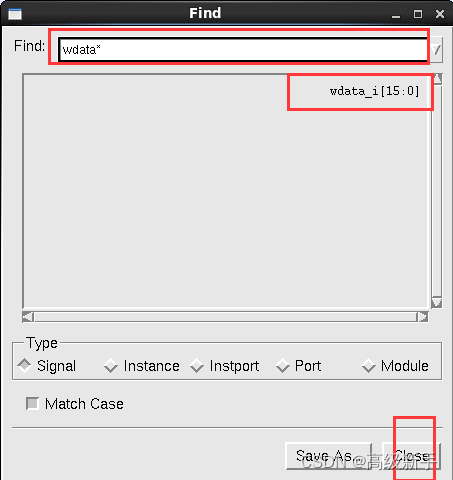

9、如何查看设计有哪些信号?【重点】

通过最右下方signal_list来查看,可以选择查看输入/输出等端口类型。

4.nSchema

1、如何打开原理图

选中设计 -> new schematic

2、如何查看nShema Window中符号对应的源代码?

双击对应的功能单元电路图,即可跳转到描述该单元的源代码

3、如何显示原理图中的各个信号/端口/模块名?

4、如何在当前的层次中查找某个信号?

被查到的信号会高亮

5、使用 Fan-In Cone追踪某个信号的驱动逻辑?

①首先要用上面的办法来查找信号,高亮选中

②调用该工具:

这样就可以看到某个信号是如何生成的(可以通过View选项来显示信号名)

6、如何产生 partial hierarchy schematic?

用来查看与选择特定信号有关的逻辑/模块

①选择需要查看的信号(可以通过shift键来选择多个信号)

②:

选择查看与wclk和wrst_n有关的信号/模块/逻辑:

7、如何移动原理图中的器件?

鼠标左键选中,按住右键进行拖拽。

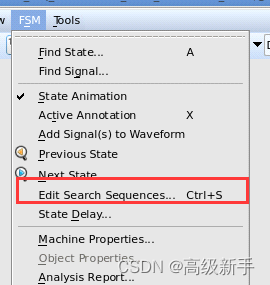

5.nState

状态机查看器。

很多设计的控制器,状态机组成。

使用Verdi流程。当拿到一个设计时,你想知道他是怎么工作的?可通过下面操作研究?

1、如何查看状态机视图?

①打开原理图

②双击相应状态机视图后,呈现状态机图

2、如何查看状态的执行语句?[重点]

3、如何查看状态的转移条件?

4、如何查看状态以及节点的相关源代码?【重点】

选择状态,然后使用鼠标中键拖拽状态到nTrace中的源代码视图中即可

5、查看在什么时候状态机转移到某个状态?《与tb有关》

①要依靠tb

②打开nstate后,要导入波形

③

6、查看某一种状态转移【状态循环】情况是否会发生?

7、如何查看某个状态被执行了多少次?《与tb有关》

8、如何查看某个状态转移到某个状态的转移次数《与tb有关》

5.nWare使用

1、添加波形到nWave

①我们要打开.v文件

②打开nWave然后打开.fsdb波形文件③正式添加波形:

-快捷键G或者:

2、添加信号到波形【重要】

-在nTrace中选中信号后,鼠标中键拖拽,或者ctrl+w进行添加

3、查找某信号,添加到nWave中?【重要】

①通过nTrave查找到该信号

②通过上面的方法进行添加

或者通过get signal来查找

4、如何给Group重命名,排序,以及调整信号位置?重命名:

信号的拖拽:

通过鼠标中键进行拖拽。

5、 缩小:【重要】

快捷键z,或者100%匹配:F

6、放大:【重要】

左键拖选放大范围

shift+Z

ctrl+滑轮:进行放大或者缩小7、移动:【重要】

鼠标中键按住信号拖拽

中键选择位置:

8、复制:

ctrl+P,或者右击信号,选择复制的选项

9、粘贴:

ins键,或者右击信号,选择粘贴的选项

(注意:可以通过鼠标中键选择粘贴的位置)10、删除:【重要】

delete键

11、改变信号的颜色:【重要】

第一步:Tools->preferences->waveform->viewoption->waveformpane->general->paint waveform

with specified color/pattern

第二步:选中信号,然后按快捷键C改变信号颜色:

12、查看信号及变化:【重要!】

任意值:所有信号变化,一般会应用到组合逻辑的指示信号

信号沿:用于查找有效指示信号,比如使能信号

总线值:主要是用来查找数据信号

模拟值:查看比如函数发生器产生的正弦波信号进制之间的转换:

符号数之间的转换:

状态寄存器显示为状态名字:

nTrace:

或者nWave

可以通过移除关联从状态机名字恢复到原来的进制显示:

可以看到,我们打开过状态机视图之后,我们也就可以在状态名和进制之间转换了:

13、如何通过逻辑操作创建新信号?

14、如何添加marker?

shift+M

15.总线操作:

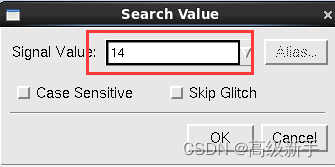

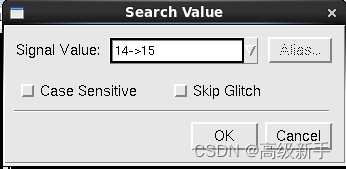

16、如何查找信号的某个值、某个值跳转到某个值?

17、如何对比两个波形?

-

相关阅读:

期货开户几条建议帮助你

【工具】lint检测工具

# 基于MongoDB实现商品管理系统(2)

一次电话面试的记录

旅游推荐系统

久运恒远链接品牌和物业建设开拓新赛道

数据结构:lambda表达式

Pytorch实现基于LSTM的情感分析

ThinkPHP框架使用工厂模式对接多个物流公司下单接口架构示例(php7.0及以上)

Masa Blazor in Blazor Day

- 原文地址:https://blog.csdn.net/Arvin_ing/article/details/127885457