-

【FLASH存储器系列十】ONFI数据接口的时序参数与时序图

👉个人主页: highman110

👉作者简介:一名硬件工程师,持续学习,不断记录,保持思考,输出干货内容

目录

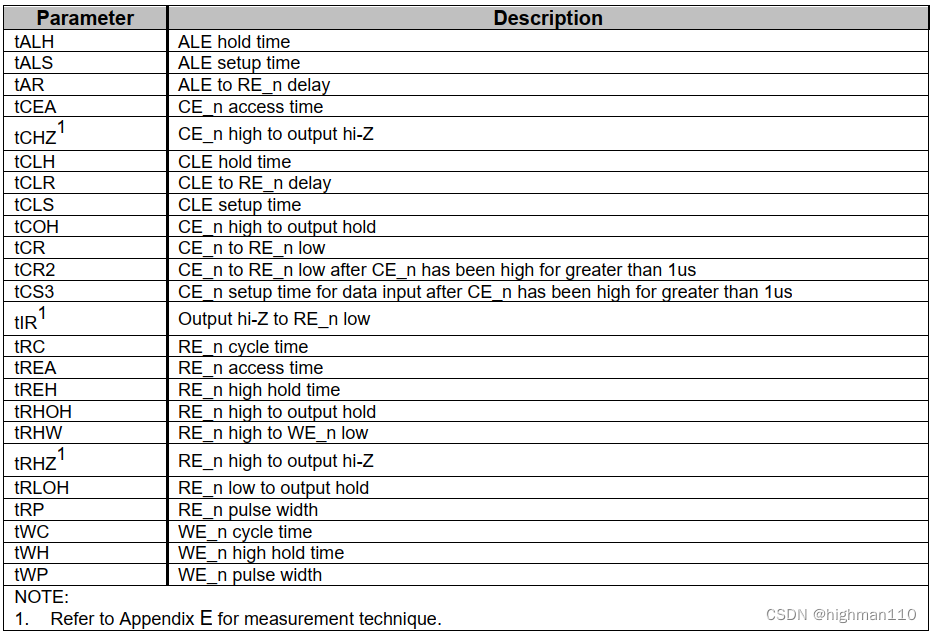

1.1 时序参数

ONFI协议中明确规定了时序参数的范围,如果不满足要求的最小和最大时序参数时,闪存设备的行为是不确定的。SDR、NV-DDR接口模式下有6种时序,NV-DDR2、NV-DDR3、NV-LPDDR4有22种时序模式,上电后闪存设备处于模式0状态下,闪存设备可以不支持所有时序模式,判断设备是否支持更高时序模式的方法是通过读取闪存的参数页。

SDR、NV-DDR、NV-DDR2、NV-DDR3、NV-LPDDR4各自有一些不同的时序参数,这里只针对SDR和NV-DDR参数进行说明,其他的接口类似,大家可以自行查阅标准文档。

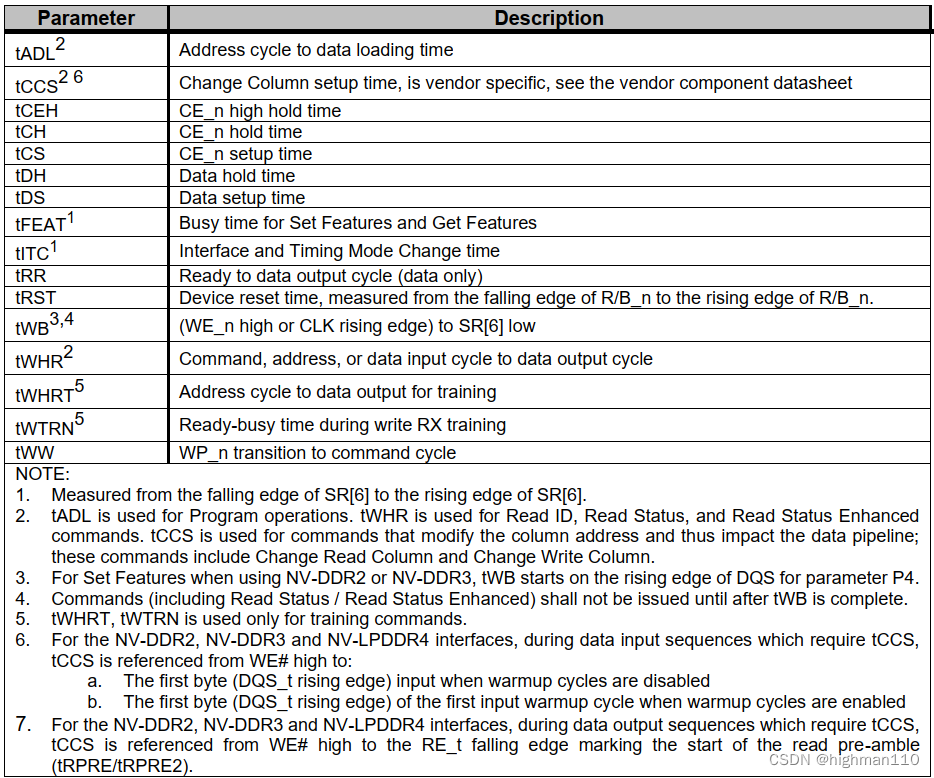

下表为SDR、NV-DDR、NV-DDR2、NV-DDR3、NV-LPDDR4共有的时序参数:

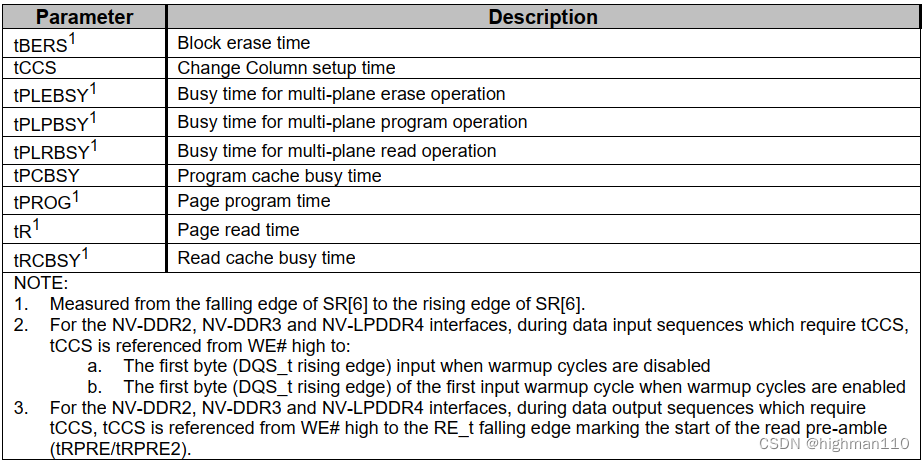

下表为阵列时序参数,这些参数是固定的,具体查看芯片的datasheet。

(tRCBSY,tPCBSY)这两个busy 时间与 cache 操作关联,(tPLEBSY,tPLPBSY,tPLRBSY)这三个busy时间与多层操作关联。这些 busy 时间的典型值和最大值如下表:

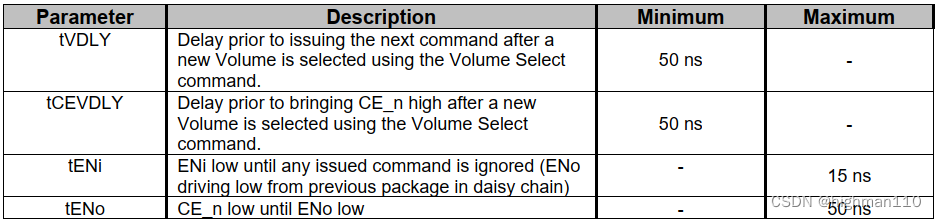

CE_n引脚减少机制可能被用于任何接口中。 如果 VccQ=3.3V 或 1.8V,则 CE_n 引脚reduction的配置应该使用 SDR 接口完成。如果 VccQ=1.2V, CE_n 引reduction 的配置应该使用 NV-DDR3 接口完成。在封装内的 daisy chain使用的enumeration信号时序以及 Volume 寻址的时序参数如下表所示。

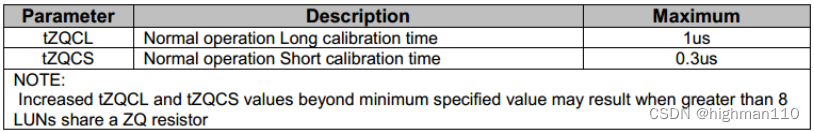

ZQ校准的时序参数如下表,SDR和NV-DDR没有ZQ校准:

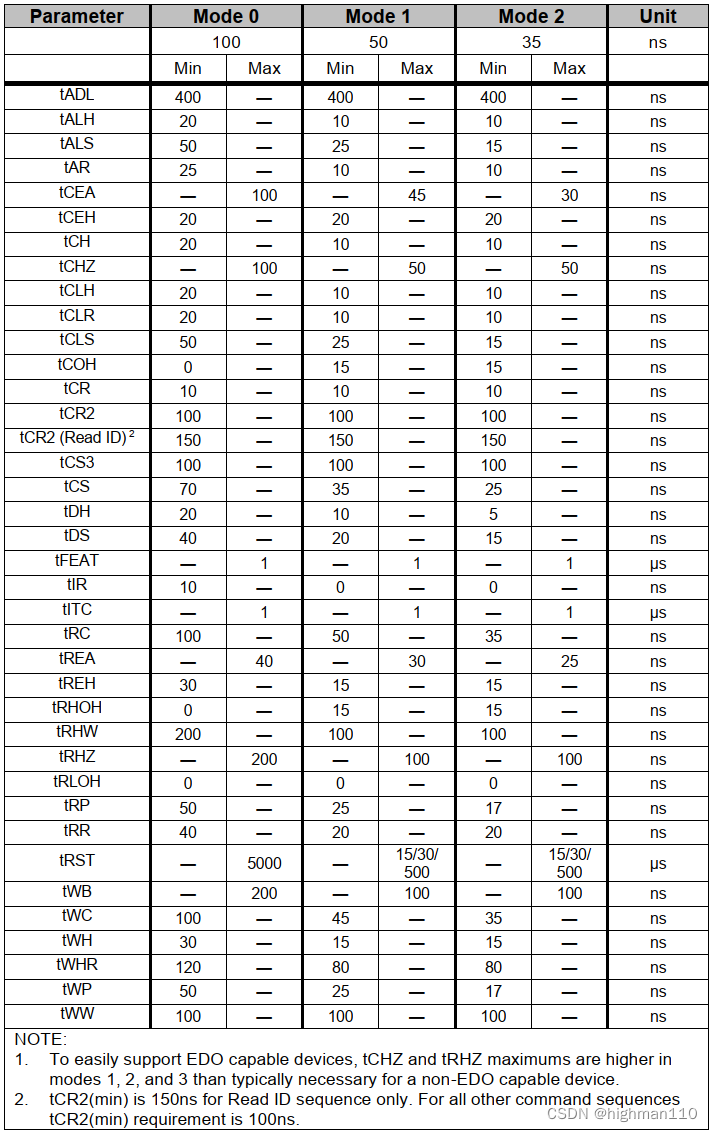

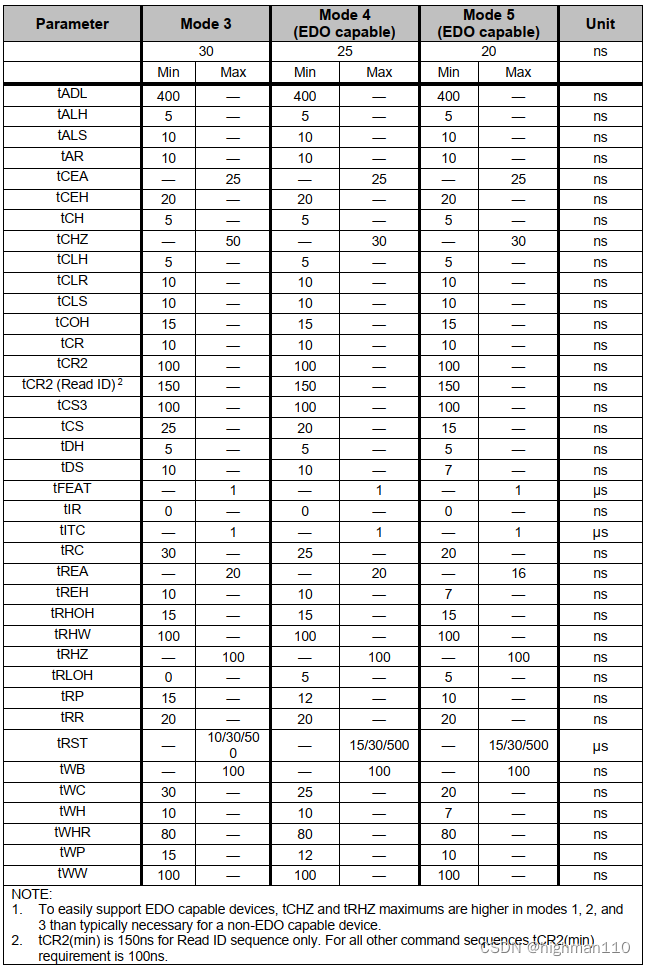

SDR的时序参数如下:

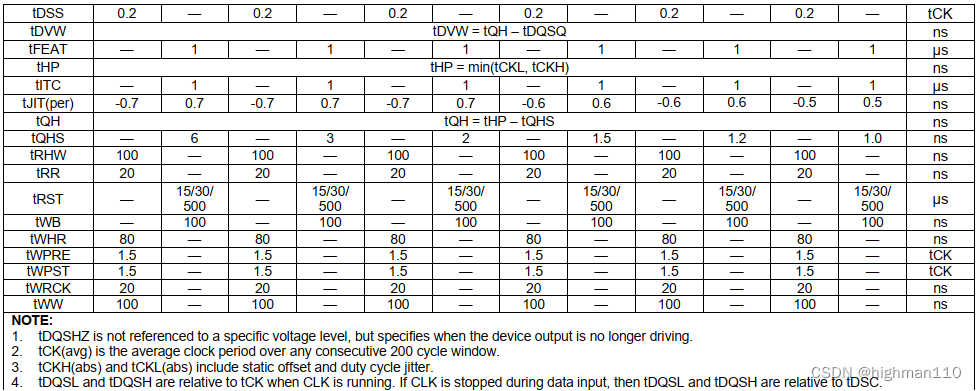

NV-DDR的时序参数如下,所有NV-DDR接口的时序参数都是以CLK的上升沿或者 DQS的锁存沿为基准。注意, R/B_n和WP_n始终是异步信号。对于按时钟测量的参数(如 tDSH),参数分别从CLK或DQS的锁存沿开始测量。

以下两张表为SDR六种时序模式下的参数值:

下表为NV-DDR六种时序模式下的参数值:

1.2 时序图详解

时序图分析仅以SDR接口为例。

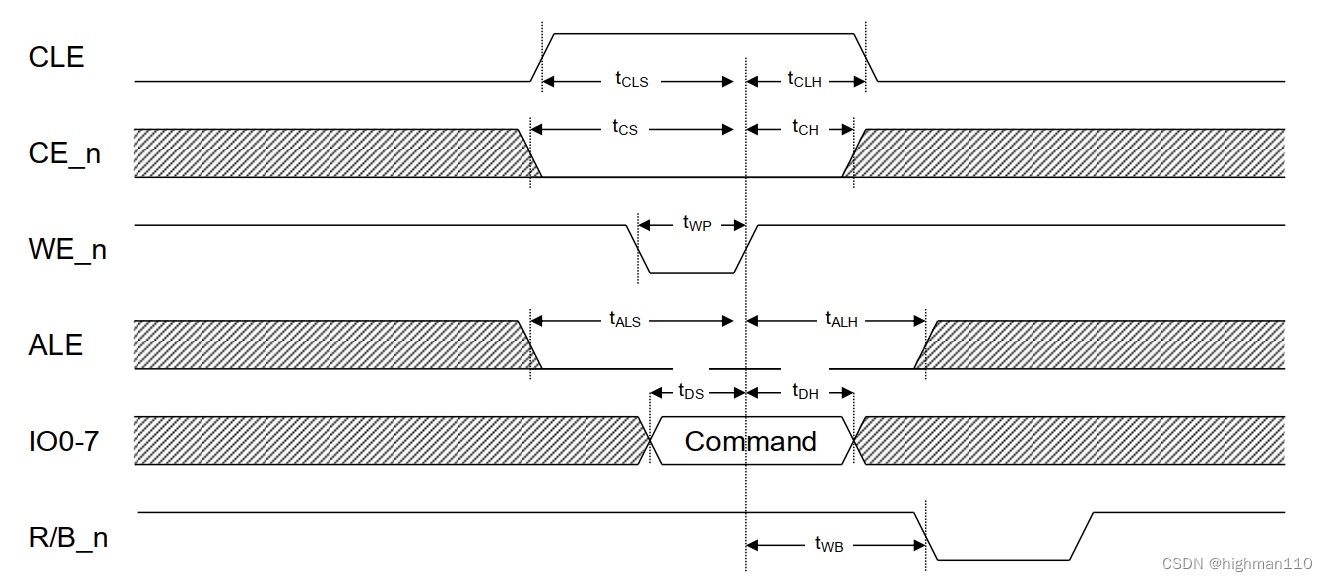

1.2.1命令锁存时序

命令锁存是在CLE为高、ALE为低时,在WE_n的上升沿锁存IO引脚上的命令值。时序图如下:

tCLS:CLE建立时间

tCLH:CLE保持时间

tCS:片选建立时间

tCH:片选保持时间

tWP:写使能脉冲宽度

tALE:ALE建立时间

tALH:ALE保持时间

tDS:数据建立时间

tDH:数据保持时间

tWB:写使能拉高到SR[6]为低(写完命令后,有一段时间flash是无法接收命令的)

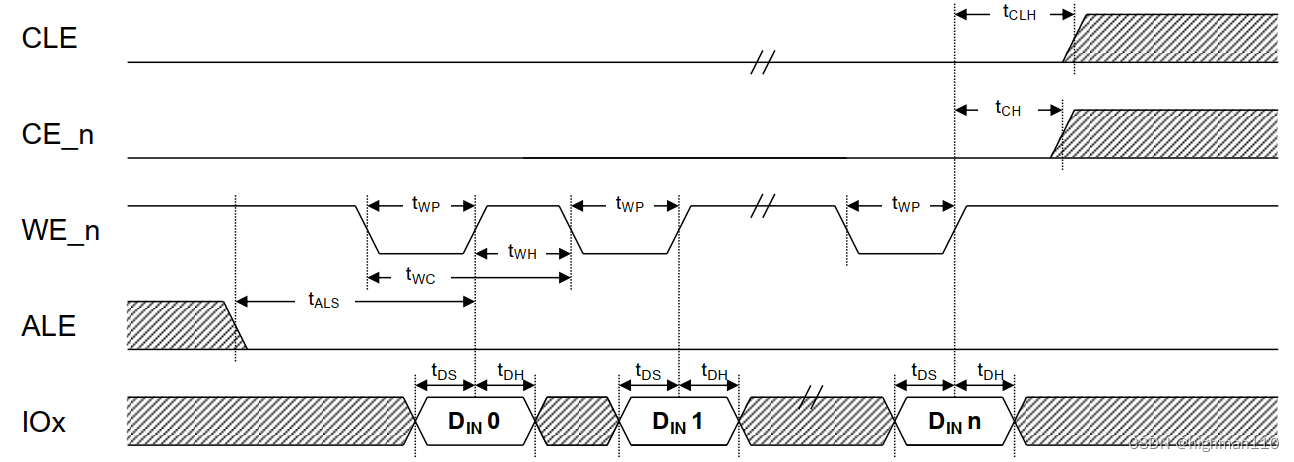

1.2.2地址锁存时序

地址锁存是在ALE为高、CLE为低时,在WE_n的上升沿锁存IO引脚上的地址值。时序图如下:

tCLS:CLE建立时间

tCS:片选建立时间

tWC:写使能周期

tWP:写使能脉冲宽度

tWH:写使能高电平保持时间

tALE:ALE建立时间

tALH:ALE保持时间

tDS:数据建立时间

tDH:数据保持时间

1.2.3数据输入时序

在CLE、ALE、片选为低时,数据在写使能信号的上升沿写入数据寄存器中。

参数含义同上。

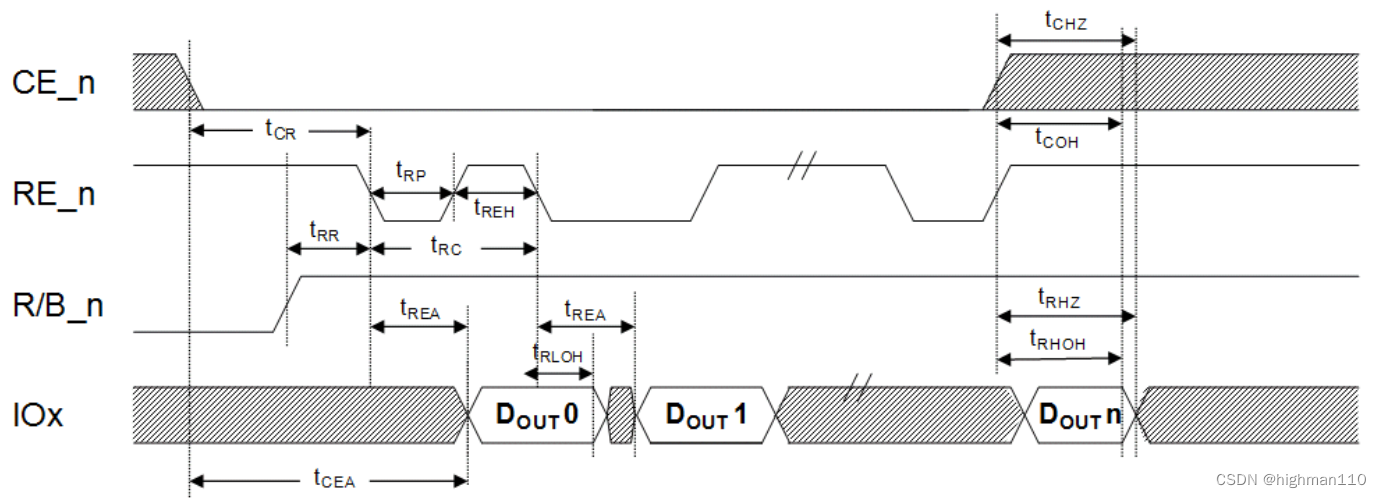

1.2.4数据输出时序

在CLE、ALE、片选为低时,数据在读使能信号的下降沿延迟一段时间后输出到IO上。

tCEA:片选接受时间

tCHZ:片选拉高到输出高阻

tCR:片选有效到读使能有效

tRP:读使能脉冲宽度

tCOH:片选拉高后的输出保持时间

tRR:ready准备好到数据可以输出的间隔

tRC:读使能信号周期

tREH:读使能高电平保持时间

tRHOH:读使能拉高后的输出保持时间

tRHZ:读使能拉高到输出高阻

tREA:读使能到数据可以输出

1.2.5数据输出时序(EDO)

在读使能信号周期小于30ns时,适用此时序图:

tRLOH:读使能拉低后的输出保持时间

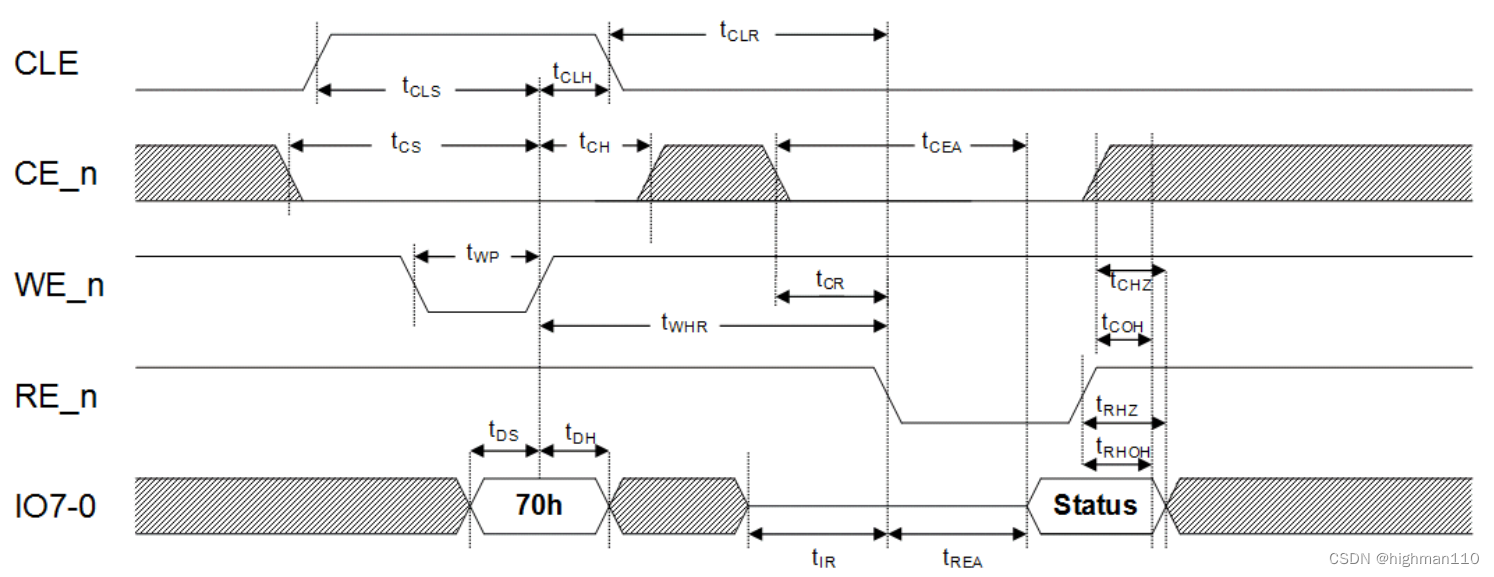

1.2.6读状态时序

相当于一段命令锁存时序,一段数据输出时序。在写使能上升沿将读状态命令70h锁存,经过一段时间后将状态寄存器SR的值输出到IO上。

tWHR:命令、地址、数据输入周期到数据输出周期的间隔

tIR:输出高阻到读使能拉低

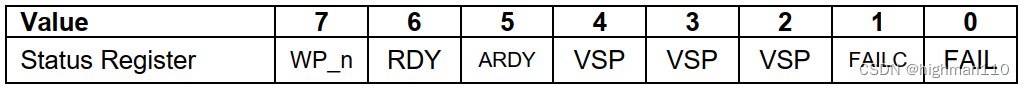

状态寄存器SR定义:

如果RDY位被清 0,则状态byte中所有其他位(除WP_n外)都是无效的,host应忽略这些值。

FAIL

如果为1,则表示上一个命令失败。如果为 0,表示上一个命令成功。对于raw NAND操作,该位只在编程或擦除操作时有效。对于EZ NAND操作,该位在读、编程以及擦除操作中有效。在program cache操作期间,该位仅当 ARDY 为1时有效。在支持ZQ 校正的device中,如果ZQ校正失败,则该位被设为1。

FAILC

如果为1,则上一个命令的前一个命令失败(上上个命令)。如果该位为0,在上一个命令的前一个命令成功。该位仅在program cache操作中有效。在Page Cache Program序列中,该位直到第二个15h命令或10h命令被发送后才会有效。如果不支持program cache 操作,则该位不会使用,应被清0。对于EZ NAND操作,该位不被使用(EZ NAND不支持cache命令)。

ARDY

如果为1,则表示没有正在进行的阵列操作。如果为0,表示某个命令正在被执行(RDY被清为0),或正在进行一个阵列操作。如果不支持重叠多层操作(overlapped multi-plane)或cache命令,则该位不会被使用。

RDY

如果为1,表示另一个命令的 LUN 或层地址已经准备好,并且状态值中所有其他位都有效。如果为0,则表示发送的上一个命令还没有执行完,并且SR[5:0]位是无效的,应该被 host 忽略。该位会影响R/B_n 的值,参见 2.18.2(R/B_n 是对应NAND target或Volume上所有LUNs的SR[6](状态寄存器bit6)的值的逻辑与。例如,R/B3_n是所有CE3_n上LUNs的SR[6]值的逻辑与。因此,R/B_n 反映的是特定NAND target上的任何LUN是否处于busy状态)。当cache操作正在进行时,该位表示另一个命令是否可被接受,而ARDY表示上一个操作是否完成。

WP_n

如果为1,则表示 device 不是写保护的。如果为0,表示device是写保护的。不论RDY位是什么值,该位都始终是有效的。

VSP

供应商定义

-

相关阅读:

ArcGIS API for JavaScript官网解析

EL表达式与JSTL标签

成功解决/bin/sh: cc: command not found和/bin/sh: g++: command not found

Spring MVC和Spring Boot

FFmpeg例子分析---音频解码decode_audio

算法-猜字母

js数据结构算法[栈操作]

k8s中calico网络组件部署时一个节点一直处于Pending状态

MySQL篇—执行计划介绍(第二篇,总共三篇)

使用tc命令模拟linux网络延迟环境

- 原文地址:https://blog.csdn.net/highman110/article/details/127909051