-

Quartus中运用多种方式设计一个D触发器,并进行仿真,时序波形验证

前言

环境要求:

Quartus Prime 18.0

modelsim 10.5

一、D触发器介绍

1、D触发是什么?

D触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。

因此,D触发器在数字系统和计算机中有着广泛的应用。触发器具有两个稳定状态,即"0"和"1",在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态。

D触发器有集成触发器和门电路组成的触发器。触发方式有电平触发和边沿触发两种,前者在CP(时钟脉冲)=1时即可触发,后者多在CP的前沿(正跳变0→1)触发。

D触发器的次态取决于触发前D端的状态,即次态=D。因此,它具有置0、置1两种功能。

对于边沿D触发器,由于在CP=1期间电路具有维持阻塞作用,所以在CP=1期间,D端的数据状态变化,不会影响触发器的输出状态。2、结构

D触发器(data flip-flop或delay flip-flop)由4个与非门组成,其中G1和G2构成基本RS触发器。电平触发的主从触发器工作时,必须在正跳沿前加入输入信号。如果在CP高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。而边沿触发器允许在CP触发沿来到前一瞬间加入输入信号。这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。边沿D触发器也称为维持-阻塞边沿D触发器。边沿D触发器可由两个D触发器串联而成,但第一个D触发器的CP需要用非门反向。

-

结构图

-

功能表

-

方程

-

时序图

二、自定义D触发器

1、创建Quartus项目

下面两种方式均可以进行创建

- 点击next

- 设置项目路径及项目名,然后next

- 选择一个空项目,next

-

next

-

芯片选型:EP4CE6F17C8

-

EDA设置

- 检查配置并点击finish

2、自定义D触发器原理图

- 打开原理图编辑窗

- 双击编辑界面,在弹出的框框里左边的文件夹寻找需要的元件,或者通过Name进行查找:

注意:

D触发器需要4 个 nand2 与非门,1 个 not 非门,2个输入管脚和2个输出管脚:

然后第一次连线就用下面这个吧,其他我用起来生成的效果图是错的,然后就是连的时候释放的点不对也会出现x,再者就是选择元件之后,不需要了可以点击Esc重置,不然他一直会携带那个元件。

- D触发器:

- 点击保存

3、编译

- 点击下面三角进行编译

- 查看硬件电路图

- 效果

4、波形仿真

注意:

仿真分为功能仿真和时序仿真,两者有什么不同?1、进行时间不同

1、功能仿真:功能仿真是在布线前进行。

2、时序仿真:时序仿真是在布线后进行。

二、关注不同

1、功能仿真:功能仿真仅仅关注输出和输入的逻辑关系是否正确,不考虑时间延时信息。

2、时序仿真:时序仿真不仅关注输出和输入的逻辑关系是否正确,同时还计算了时间延时信息。

三、要求不同

1、功能仿真:功能仿真了解实现的功能是否满足设计要求,其仿真结果与电路设计的真值表的结果相对应。

2、时序仿真:时序仿真了解实现的功能是否满足真实器件运行的要求,与特定的器件有关。-

新建波形文件

点击File->new

-

在弹出的窗口双击空白的地方,然后点击Node Finder:

-

在随后出现的“node finder”对话框中点击“list”按钮,则半加器中所有的输入输出引脚全部出现在对话框左边。再在该界面上点击“>>”,则把左边所有的端口都选择到右边,进入波形:

-

点击两次ok进行返回,随后出现下面波形图:

- 点击CLK设置时钟信号

- 左键对D波形进行选中,设置为高电平

-

保存到相应路径

- 功能仿真

-

功能仿真图:

从图中看出Q比D延迟了半个时钟周期,这是因为Q在D处于上升沿才有反应。

- 时序仿真

- 时序仿真图

输出变化延时了一个时钟周期

三、调用D触发器

省略创建工程步骤,之间来到选择元件的步骤。

1、调用D触发器的原理图

-

输入dff查找D触发器元件

-

原理图

-

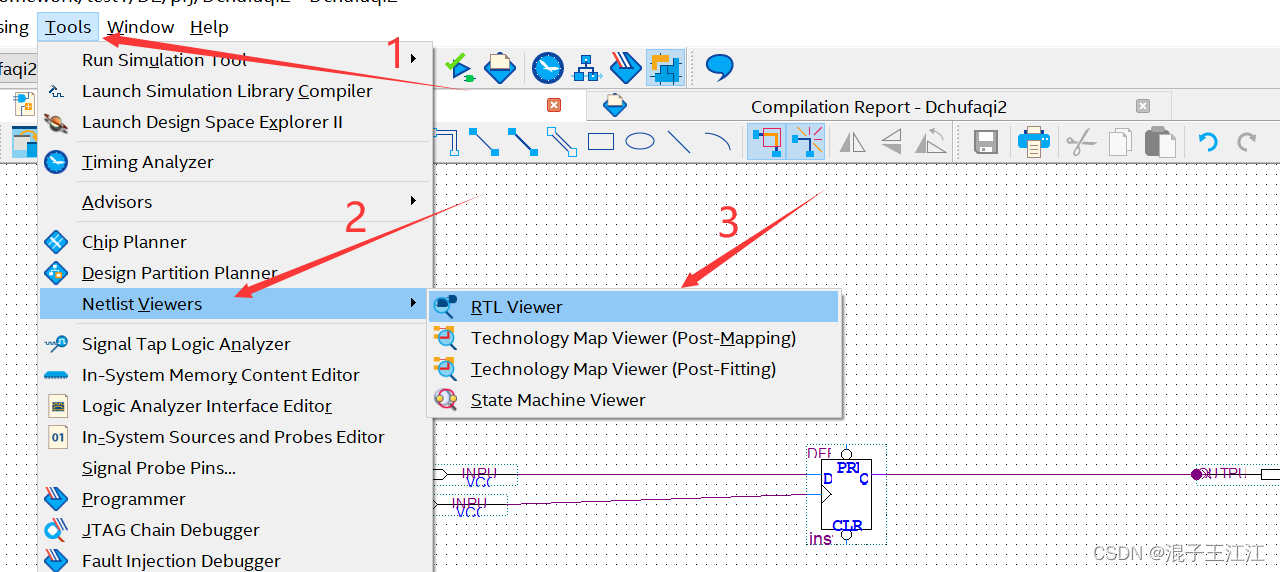

查看硬件连接图:

2、仿真图

-

原图:设计一部分高电平

-

功能仿真图:

-

时序仿真图:

效果与自定义的一致,功能仿真波形图延迟半个时钟周期,时序仿真图延迟一个时钟。

四、Verilog语言实现一个触发器

与前面一样,创建一个工程。

1、创建一个Verilog HDL 文件

File->new:

2、配置代码

//Dchufaqi3是文件名 module Dchufaqi3(D,CLK,Q); input D; input CLK; output Q; reg Q; always @ (posedge CLK)//我们用正的时钟沿做它的敏感信号 begin Q <= D;//上升沿有效的时候,把d捕获到q end endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

3、编译

- 保存->编译->查看硬件原理图

4、仿真图

- 功能仿真

- 时序仿真

效果同样与前面一致,功能仿真波形图延迟半个时钟周期,时序仿真图延迟一个时钟。

五、总结

复习了D触发器,从自定义触发器到调用到脱离,越来越抽象,越发体会到通过Verilog语言进行硬件电路开发的便捷。

六、参考资料

https://blog.csdn.net/weixin_46129506/article/details/123443865

https://baike.baidu.com/item/D%E8%A7%A6%E5%8F%91%E5%99%A8/10169294 -

-

相关阅读:

技术风向标 | 云原生技术架构成熟度模型解读

最优化 | 一维搜索与方程求根 | C++实现

python-继承

window删除文件夹时提示源路径太长无法删除的解决办法

前端笔记(10) Vue3 Router 监听路由参数变化

Error: svn: E155004: Run ‘svn cleanup‘ to remove locks

云计算与 openstack

SpringBoot bbs(3~4) 过度创作总结。

【pen200-lab】10.11.1.13

SylixOS---Qt 桌面级应用进程通信

- 原文地址:https://blog.csdn.net/qq_52215423/article/details/127832959