-

【计算机组成原理】电路基本原理、加法器的设计

ALU

算术运算:加减乘除等

逻辑运算:与、或、非、异或等

辅助功能:移位、求补等

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-FxFq9wpM-1668229678047)(C:\Users\17215\AppData\Roaming\Typora\typora-user-images\image-20221112124455065.png)]](https://1000bd.com/contentImg/2024/04/24/dd21539493a912e9.png)

M S为来自CU控制单元的信号

A和B为两个4bit的数据输入,F为4bit数据的输出

机器字长和ALU位数,输入数据位数和其他寄存器位数相同

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-qQYNqKiq-1668229678048)(C:\Users\17215\AppData\Roaming\Typora\typora-user-images\image-20221112124524098.png)]](https://1000bd.com/contentImg/2024/04/24/30e47e6904ef3b07.png)

逻辑运算和门电路

下面的门电路,分别展示了与门,或门,非门。

一般非都会有个小⭕在前面。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-Q5n2Y3uV-1668229678049)(C:\Users\17215\AppData\Roaming\Typora\typora-user-images\image-20221112124838374.png)]](https://1000bd.com/contentImg/2024/04/24/850554f05ac476b1.png)

优先级:与>或(类比加减乘除)

Ex:实现AC+AD

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-FR2tsxTW-1668229678049)(C:\Users\17215\AppData\Roaming\Typora\typora-user-images\image-20221112125208167.png)]](https://1000bd.com/contentImg/2024/04/24/7bf0546d18d1bd44.png)

异或的逻辑表达与门电路:

同或是异或取反

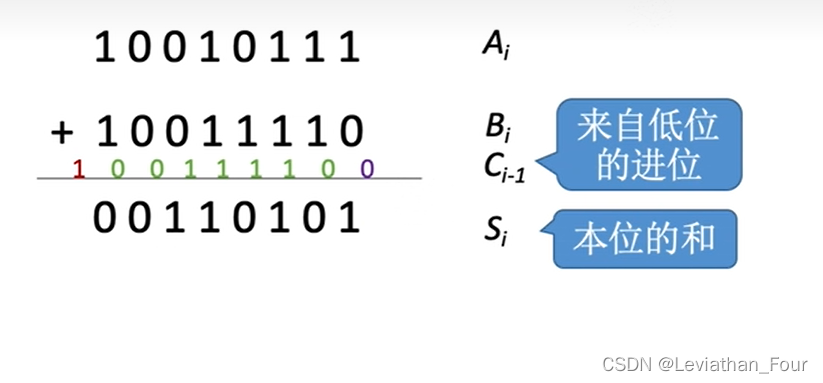

一位全加器

我们可以将加法化为4个元素的有机结合

每一步的C和S和这一步的A、B以及上一步的C有关。相关逻辑运算如下:

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-55yLWpij-1668229678052)(C:\Users\17215\AppData\Roaming\Typora\typora-user-images\image-20221112125759001.png)]](https://1000bd.com/contentImg/2024/04/24/d27a7127f4e90bde.png)

相应的门电路:

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-g5p423ss-1668229678052)(C:\Users\17215\AppData\Roaming\Typora\typora-user-images\image-20221112125839726.png)]](https://1000bd.com/contentImg/2024/04/24/e457ad7f33bb4d5e.png)

一位全加器:

串行加法器:

只有一个加法器,数据逐行传入运算,进位触发器保留进位数,参与下一次运算。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-WmtPXh7i-1668229678054)(C:\Users\17215\AppData\Roaming\Typora\typora-user-images\image-20221112130051977.png)]](https://1000bd.com/contentImg/2024/04/24/2ed4a4649832c64c.png)

串行进位的并行加法器(行波进位)

把n个全加器串接起来,直接进行两个n位数的相加

more

带组内运行的是将结果根据之前的数据直接运算得出,不需要等输出过来得数据了。

组内并行,组间串行

组内并行,组间并行

-

相关阅读:

计算机毕业设计(附源码)python在线阅读系统

35.【C/C++ 枚举(bool)类型和宏定义 (超详细)】

大家一起来学习如何使用spring.factories

【面试题】http协议

多方面浅谈互联网技术

Centos 下mysql数据库完整安装过程(亲测可用)

升级Openssl 1.1.1版本以及更新Nginx应用新版Openssl

【PAT甲级】1082 Read Number in Chinese

MQTT-保留消息和遗嘱消息

MyBatisPlus一个依赖轻松搞定权限问题

- 原文地址:https://blog.csdn.net/weixin_45755831/article/details/127819080