-

【DSPF8003x】 Enhanced Pulse Width Modulator (ePWM)

简介

PWM每个子模块:

- 时基子模块

- 计数器比较子模块

- 动作限定子模块

- 死区发生器子模块

- PWM斩波器(PC)子模块

- 跳闸区子模块

- 事件触发子模块

- 数字比较子模块

ePWM模块通过时钟同步方案连接在一起,允许它们在需要时作为单个系统运行。此外,该同步方案可以扩展到捕获外围设备子模块(eCAP)。子模块的数量依赖于设备并基于目标应用程序的需求。子模块也可以独立运行。

每个PWM包括以下性质:- 两个PWM输出(EPWMxA和EPWMxB),可用于以下配置:

-

- 两个独立的PWM输出,具有单边缘操作

-

- 两个独立的PWM输出,具有双边缘对称操作

-

- 一个独立的PWM输出,具有双边缘不对称操作

- 通过软件对PWM信号进行异步覆盖控制。

- 可编程相位控制支持滞后或超前操作相对于其他ePWM模块。

- 以周期为基础的硬件锁定(同步)相位关系。

- 具有独立上升和下降边缘延迟控制的死区生成。

- 可编程的行程区域分配,按周期trip和故障条件下的一次trip。

- 跳闸条件可以强制PWM输出的高、低或高阻抗状态逻辑电平。

- 所有事件都可以触发CPU中断和ADC转换开始(SOC)

- 可编程事件预缩放最大限度地减少中断时的CPU开销。

- 通过高频载波信号进行PWM斩波,用于脉冲变压器门驱动。

子模块参数说明

每个ePWM外设包括八个子模块。每个子模块执行特定的任务,这些任务可以由软件配置。

Time-Base Submodule

每个ePWM模块都有自己的基于时间的子模块,该子模块决定ePWM模块的所有事件计时。内置的同步逻辑允许多个ePWM模块的时间基础作为一个单一系统一起工作。图20-4说明了基于时间的模块在ePWM中的位置。

Trip-Zone(TZ) Submodule

图20-42显示了trip-zone (TZ)子模块在ePWM模块中的位置。

每个ePWM模块连接6个TZn信号(TZ1 ~ TZ6)。TZ1到TZ3来自GPIO mux。

TZ4来自那些带有EQEP模块的设备上的反向EQEPxERR信号。TZ5连接到系统时钟故障逻辑,TZ6来自CPU的EMUSTOP输出。这些信号指示外部故障或跳闸情况,当故障发生时,ePWM输出可编程进行相应响应。

TZ子模块作用

- trip输入TZ1到TZ6可以灵活映射到任何ePWM模块。

- 在故障条件下,输出EPWMxA和EPWMxB可以强制到以下之一:高、低、高阻抗、不采取任何行动

- 支持一次跳闸(OSHT)的主要短路或过流条件。

- 支持逐周期Trip(CBC)限流操作。

- 支持基于片上模拟比较器模块输出和/或TZ1到TZ3信号状态的数字比较跳闸(DC)。

- 每个跳闸区输入和数字比较(DC)子模块DCAEVT1/2或DCBEVT1/2力事件可以分配给单次或逐周期操作。

- 可以在任何跳闸区输入上生成中断。

- 还支持软件强制Tripping。

- 如果不需要,可以完全绕过trip-zone子模块

TZ信号TZ1到TZ6(也统称为TZn)是主动低输入信号。当其中一个信号变低时,或者根据TZDCSEL寄存器事件选择发生DCAEVT1/2或DCBEVT1/2强制时,表示发生了跳闸事件。每个ePWM模块可以单独配置,以忽略或使用每个跳闸区信号或DC事件。特定的ePWM模块使用哪个跳闸区信号或DC事件由该特定ePWM模块的TZSEL寄存器决定。Trip信号可能同步到ePWMclock (EPWMCLK),也可能不同步,并在GPIO MUX块内进行数字滤波。TZn输入上至少3*TBCLK低脉冲宽度足以触发ePWM模块的故障条件。如果脉冲宽度小于此值,则CBC或OST锁存器可能无法锁存脱扣条件。异步行程确保如果时钟因任何原因丢失,输出仍然可以由TZn输入上的有效事件触发。必须对gpio或外设进行适当的配置。

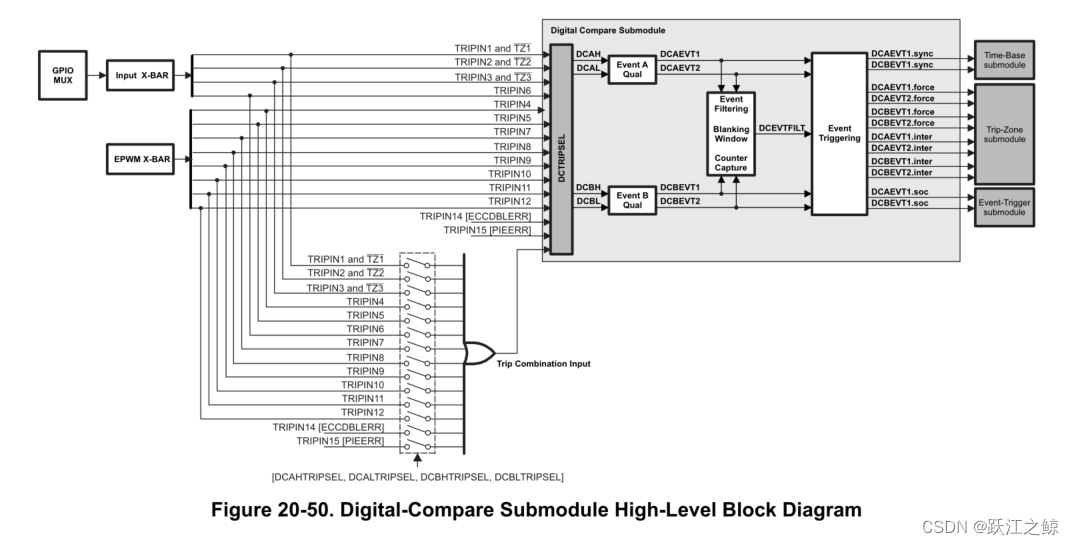

Digital Compare(DC) Submodule

图20-50说明了数字比较(DC)子模块信号与ePWM系统中其他子模块的接口位置。

eCAP输入信号来源于输入X-BAR信号,如图20-51所示。

在该设备上,任何GPIO引脚都可以灵活地映射为trip区域输入和/或trip输入到trip区域子模块和数字比较子模块。输入X-BAR输入选择(INPUTxSELECT)寄存器定义了哪些GPIO引脚被分配为trip区输入/ trip输入。

数字比较(DC)子模块比较ePWM模块外部的信号(例如,来自模拟比较器的CMPSSx信号),直接生成PWM事件/动作,然后馈送给事件触发器、跳闸区和时基子模块。此外,还支持消隐窗口功能,以过滤来自直流事件信号的噪声或不需要的脉冲。

Purpose of the Digital Compare Submodule

-

模拟比较器(COMP)模块输出通过外部输入X-BAR逻辑,使用GPIO外设,内部PIE, ECC错误信号,TZ1, TZ2和TZ3输入产生数字比较A高/低(DCAH, DCAL)和数字比较B高/低(DCBH, DCBL)信号。

-

DCAH/L和DCBH/L信号触发事件,然后可以过滤或直接提供给TZ、事件触发和基于时间的子模块,以:生成跳闸区中断、生成ADC转换开始、强制事件、生成同步事件以同步ePWM模块TBCTR。

-

事件滤波(空窗逻辑)可以选择空输入信号以去除噪声。

Using CMPSS to Trip the ePWM on a Cycle-by-Cycle Basis

当使用CMPSS在一个周期一个周期的基础上跳闸ePWM时,应该采取措施防止一个PWM周期中断言的比较器跳闸状态延伸到下一个周期。CMPSS可用于向下游ePWM模块发送脱扣状态信号。对于峰值电流模式控制等应用,每个PWM周期只需要一个跳闸事件。在某些情况下,如果不采取预防措施,持续或延迟跳闸事件(接近PWM周期的结束)可能会延续到下一个PWM周期。如果CMPSS数字滤波器或ePWM数字比较(DC)子模块被配置为限定比较器跳闸信号,在ePWM跳闸逻辑能够响应跳闸信号的逻辑变化之前,将引入“N”个限定时钟周期。一旦ePWM跳闸条件合格,跳闸条件将在比较器跳闸信号去断言后保持活动N个时钟周期。如果一个合格的比较器跳闸信号在一个PWM周期结束之前的N个时钟周期内保持断言,跳闸条件将不会被清除,直到下一个PWM周期已经开始。因此,新的PWM周期将检测跳闸条件一旦开始。

为了避免这种不希望发生的跳闸情况,用户应用程序应该采取措施,确保ePWM跳闸逻辑看到的合格跳闸信号在每个PWM周期结束之前被解除断言。

…

-

相关阅读:

雪花算法详解(原理优缺点及代码实现)

Go 语言 结构体和方法

Spring源码分析(三) bean的生命周期 createBean()和doCreateBean()

leetcode困难之1127. 用户购买平台

如何选择外贸网站服务器?

【Qt】网络通信(TCP&UDP)

Go基础18-理解方法的本质以选择正确的receiver类型

各种存储性能瓶颈分析与优化方案

Spring Security登录流程分析

java毕业设计鸿鹄教育培训(附源码、数据库)

- 原文地址:https://blog.csdn.net/qq_34551090/article/details/127727975