-

FPGA学习笔记(六)Modelsim单独仿真和Quartus联合仿真

系列文章目录

二、FPGA学习笔记(二)Verilog语法初步学习(语法篇1)

四、FPGA学习笔记(四)通过数码管学习顶层模块和例化的编写

五、FPGA学习笔记(五)Testbench(测试平台)文件编写进行Modelsim仿真

六、FPGA学习笔记(六)Modelsim单独仿真和Quartus联合仿真

七、FPGA学习笔记(七)verilog的深入学习之任务与函数(语法篇3)

Modelsim单独仿真

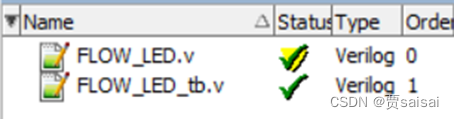

Modelsim中新建项目后,导入编写的Testbench文件和程序文件,点击compile all编译,没有错误后,点击start simulation 开始仿真。

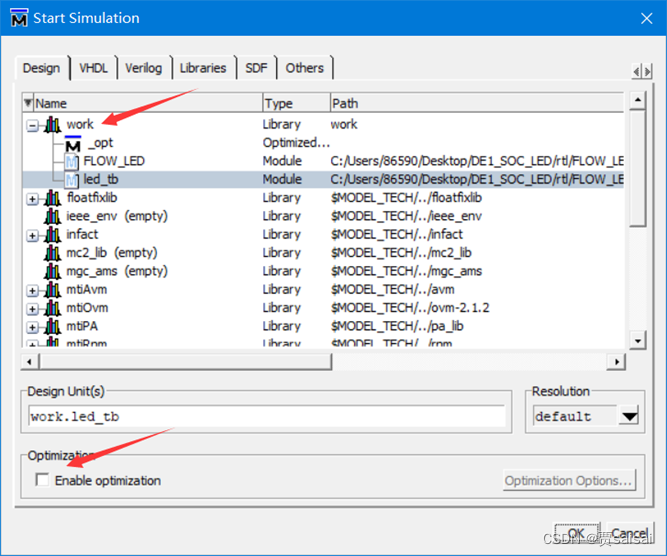

在work中选择编写Testbench时定义的仿真模块,取消勾选使能优化。

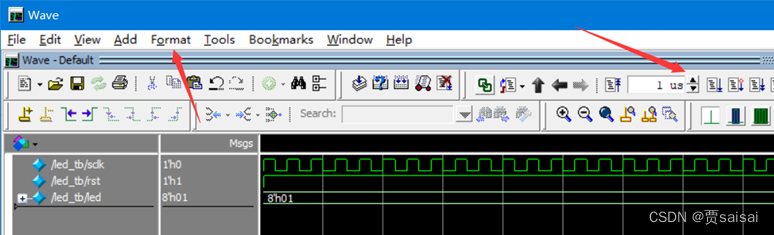

点击Add Wave添加参数的波形。

利用Format可以更改显示格式,利用快捷工具栏修改仿真时间。

Quartus联合仿真

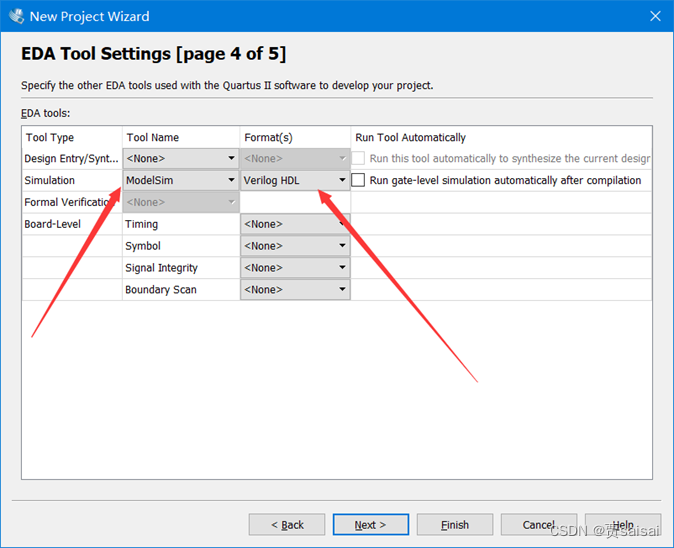

首先,需要在quartus中设置仿真的类型,可以在新建项目时设置

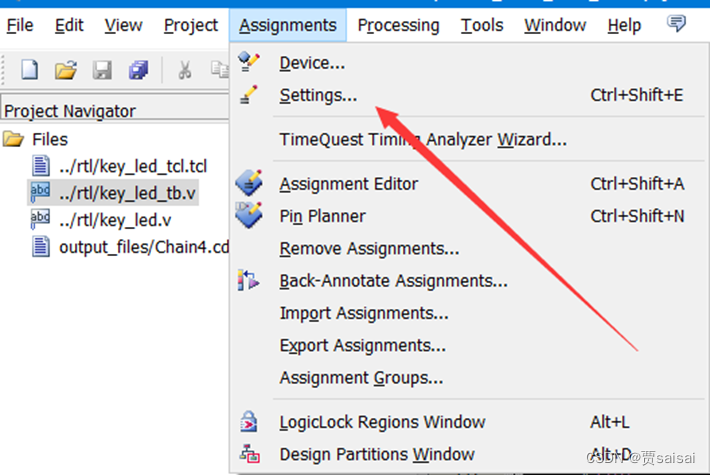

或者可以在Assignments中的Setting中设置

设置modelsim的软件路径

利用Quartus自动生成仿真文件Testbench框架

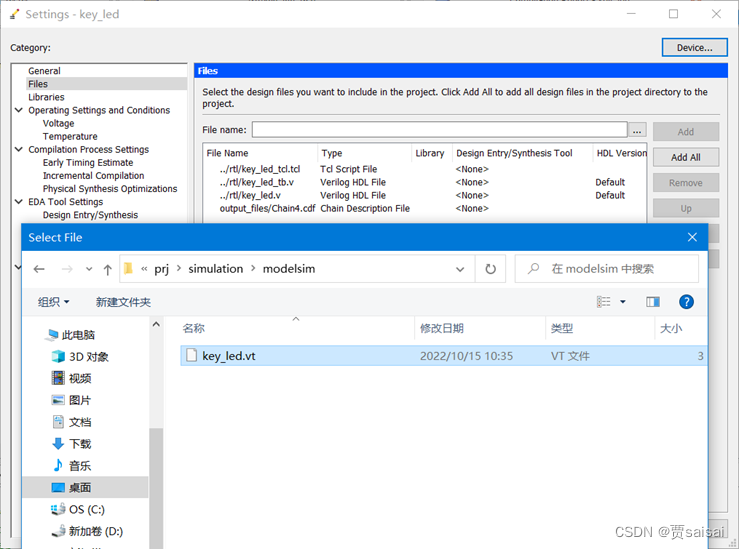

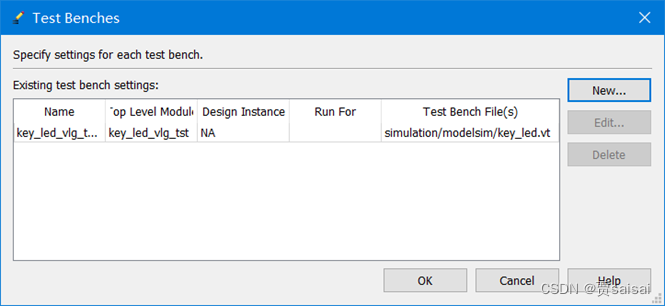

提示没有错误后,在Settings中将生成的仿真文件.vt添加到项目文件中

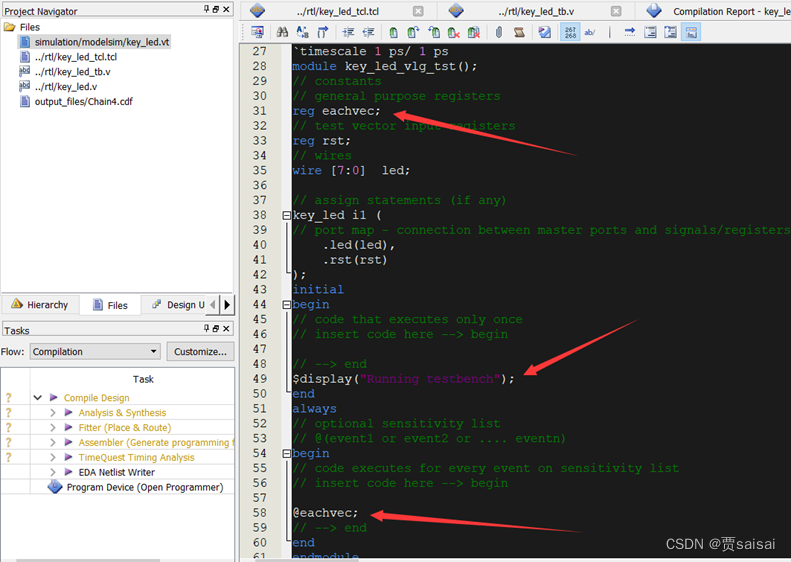

打开.vt文件后,一些红色箭头标注的不需要,然后在里面添加自己需要的内容。

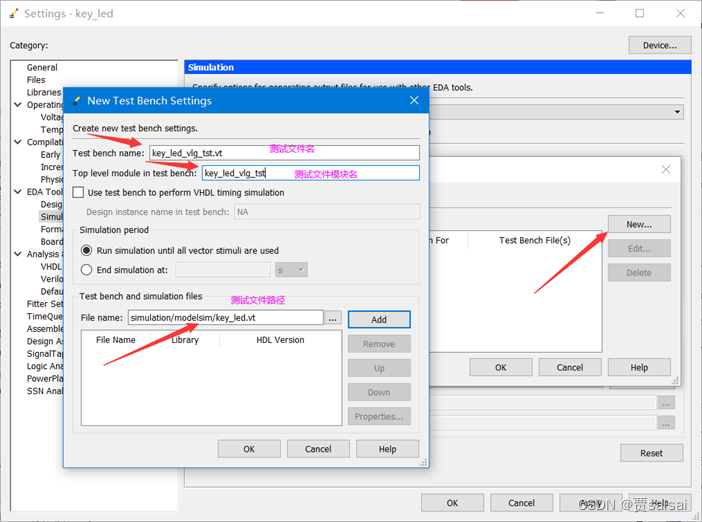

添加完成后设置编译的仿真文件

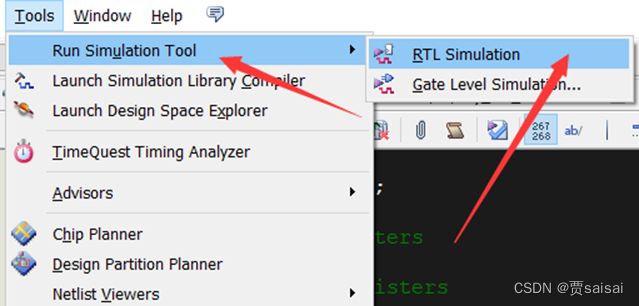

添加完成后开启仿真,quartus就会自动打开modelsim进行仿真。

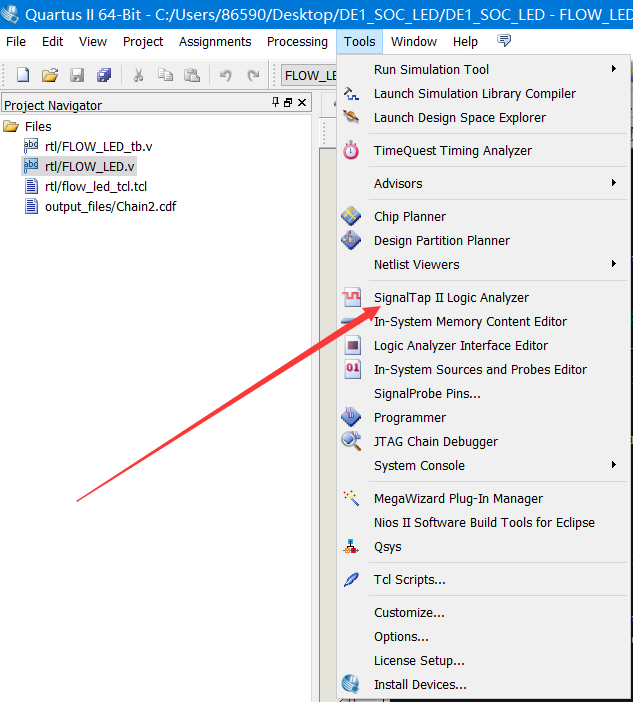

Signal Tap II使用

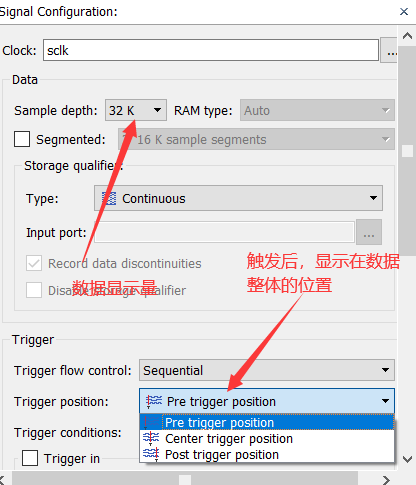

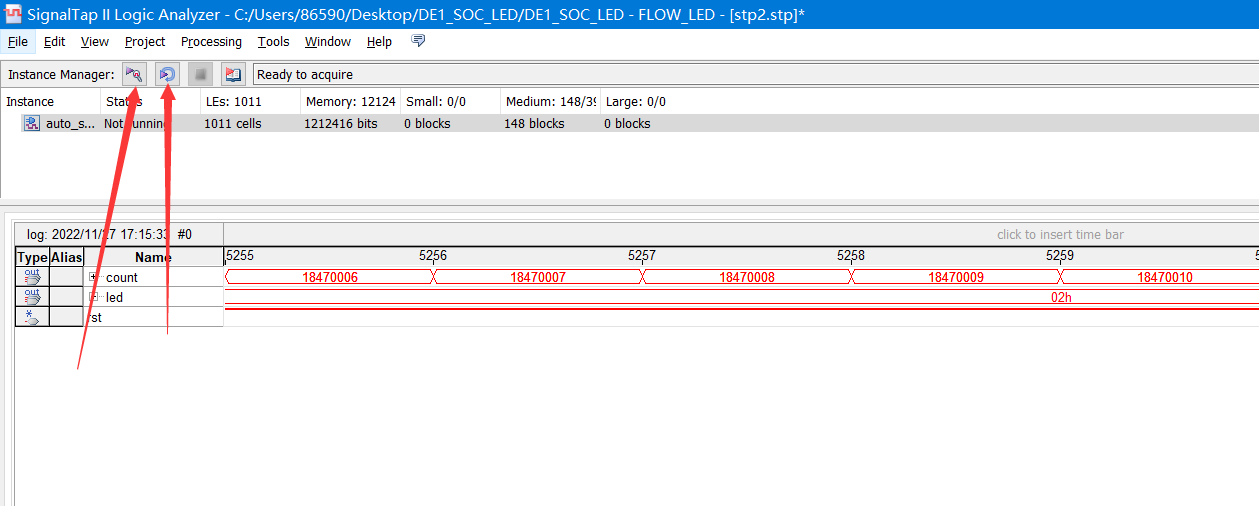

下图是设置的采样时钟,所以如果用这个时钟去采集同样频率的sclk,是采集不到的

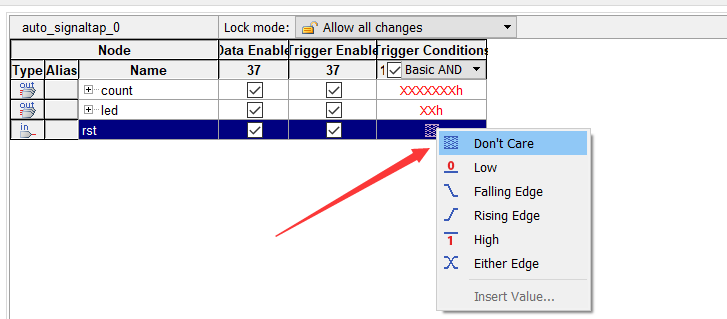

这里就可以选择按键复位的触发方式,在数据显示界面就可以看到实体按键按下前后数据的变化,结合上面的触发后数据显示位置,来观测数据

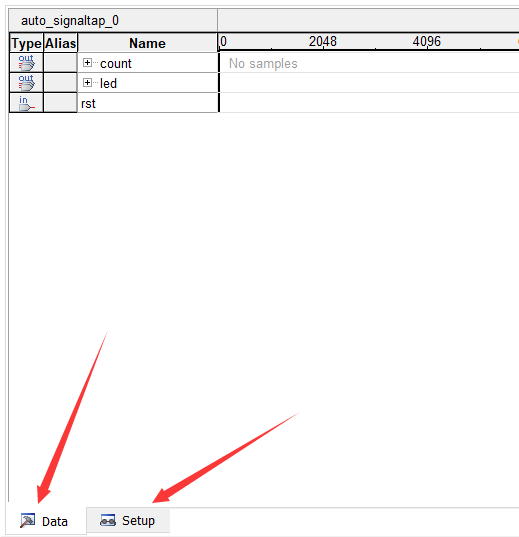

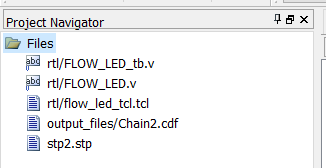

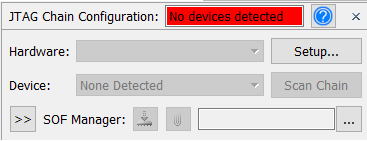

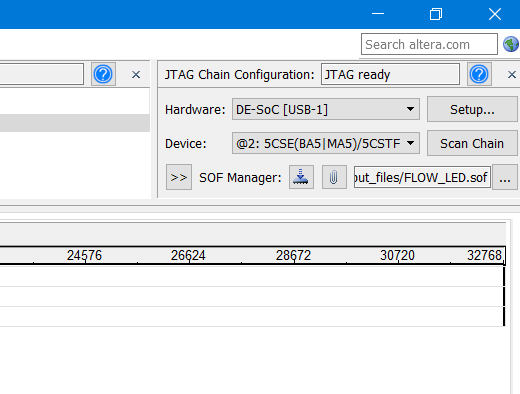

设置和数据显示切换设置完成后,保存到项目中,编译生成下载,也可以在这个界面里下载

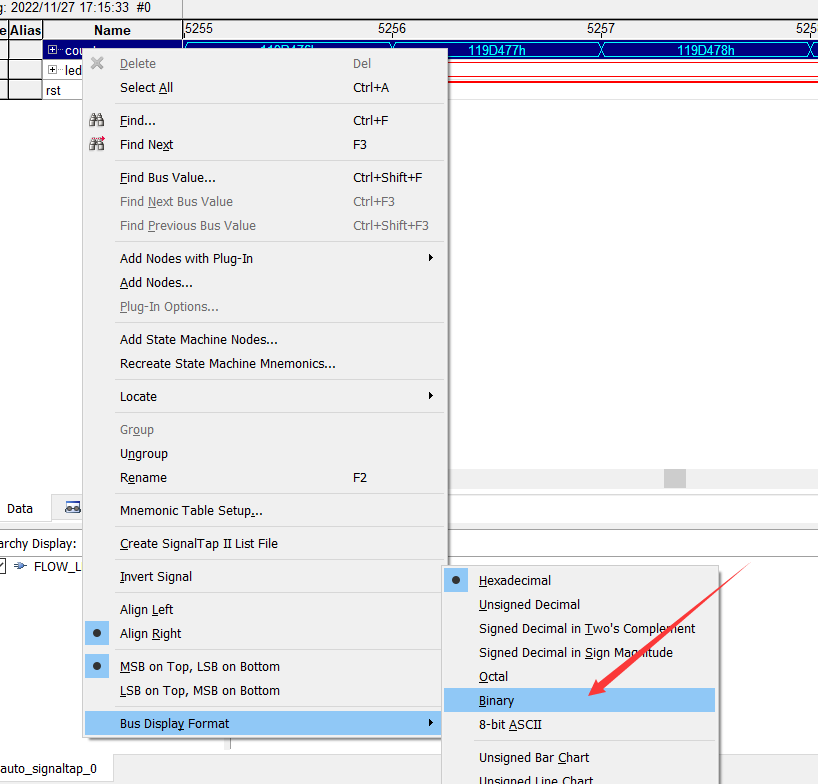

切换数据显示格式:

数据采集开始:

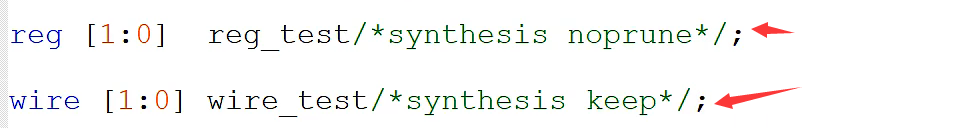

下图中/* */可以防止前面定义的信号被优化(如果编译器发现这两个变量对模块输入输出没有影响,就会优化),这样signal tap才能有这个变量。

当然如果被定义了,但是其他程序没有使用,还是没用没有这个变量

-

相关阅读:

史上最全webpack带你深入了解webpack

网络端口验证

Visual Studio 2010 配置和使用Qt5.6.3

web期末网站设计大作业 奶茶店网站美食餐饮网站设计与实现(HTML+CSS+JavaScript)

java毕业设计面向大学生心理健康服务平台源码+lw文档+mybatis+系统+mysql数据库+调试

Day31-IO流原理及流的分类、FileInputStream、FileOutputStream、文件拷贝

[附源码]计算机毕业设计JAVA车辆违章信息管理系统

最新天津python培训机构 Python培训的重要性

Java自学注意细节快速成长

采集分析仪设计原理图:437-带触摸显示的10路5Msps@18bit采集分析仪

- 原文地址:https://blog.csdn.net/zerokingwang/article/details/127336286